Difference between revisions of "Memory"

GerdIsenberg (talk | contribs) |

m (→Memory Management: added MLP) |

||

| (5 intermediate revisions by one other user not shown) | |||

| Line 133: | Line 133: | ||

* [http://www.memorymanagement.org/ The Memory Management Reference] [http://www.ravenbrook.com/ Ravenbrook] | * [http://www.memorymanagement.org/ The Memory Management Reference] [http://www.ravenbrook.com/ Ravenbrook] | ||

* [https://en.wikipedia.org/wiki/Memory_protection Memory protection from Wikipedia] | * [https://en.wikipedia.org/wiki/Memory_protection Memory protection from Wikipedia] | ||

| + | * [https://en.wikipedia.org/wiki/Memory-level_parallelism Memory-level parallelism (MLP) from Wikipedia] | ||

<span id="Virtual"></span> | <span id="Virtual"></span> | ||

==Virtual Memory== | ==Virtual Memory== | ||

| Line 261: | Line 262: | ||

* [https://en.wikipedia.org/wiki/Ken_Knowlton Kenneth C. Knowlton] ('''1965'''). ''A Fast storage allocator''. [[ACM#Communications|Communications of the ACM]], Vol. 8, No. 10 : 623-625 | * [https://en.wikipedia.org/wiki/Ken_Knowlton Kenneth C. Knowlton] ('''1965'''). ''A Fast storage allocator''. [[ACM#Communications|Communications of the ACM]], Vol. 8, No. 10 : 623-625 | ||

===1970 ...=== | ===1970 ...=== | ||

| + | * [[Paul W. Purdom]], [[Mathematician#SMStigler|Stephen M. Stigler]] ('''1970'''). ''[https://www.semanticscholar.org/paper/Statistical-Properties-of-the-Buddy-System-Purdom-Stigler/36ffdc1a3960dd9874d676176d1e4bd48c99b528 Statistical Properties of the Buddy System]''. [[ACM#Journal|Journal of the ACM]], Vol. 17, No. 4 <ref>[https://en.wikipedia.org/wiki/Buddy_memory_allocation Buddy memory allocation from Wikipedia]</ref> | ||

* [[Donald Eastlake]] ('''1977'''). ''[http://www.informatik.uni-trier.de/~ley/db/conf/vldb/Eastlake77.html Tertiary Memory Access and Performance in the Datacomputer]''. [http://www.informatik.uni-trier.de/~ley/db/conf/vldb/vldb77.html#Eastlake77 VLDB 1977] | * [[Donald Eastlake]] ('''1977'''). ''[http://www.informatik.uni-trier.de/~ley/db/conf/vldb/Eastlake77.html Tertiary Memory Access and Performance in the Datacomputer]''. [http://www.informatik.uni-trier.de/~ley/db/conf/vldb/vldb77.html#Eastlake77 VLDB 1977] | ||

===1980 ...=== | ===1980 ...=== | ||

| + | * [[Paul W. Purdom]], [[Mathematician#CABrown|Cynthia A. Brown]] ('''1980'''). ''[https://www.semanticscholar.org/paper/Exact-formulas-for-the-buddy-system-Purdom-Brown/edb813045099fe0e657d20e2c7d5b54ddbb9fbcd Exact formulas for the buddy system]''. [https://en.wikipedia.org/wiki/Information_Sciences_(journal) Information Sciences], Vol. 22, No. 1 | ||

* [[Ozalp Babaoglu]], [https://en.wikipedia.org/wiki/Bill_Joy William Joy] ('''1981'''). ''Converting a Swap-Based System to do Paging in an Architecture Lacking Page-Reference Bits''. Proceedings of the 8th SOSP, Operating Systems Review, Vol. 15, No. 5, pp. 78-86 | * [[Ozalp Babaoglu]], [https://en.wikipedia.org/wiki/Bill_Joy William Joy] ('''1981'''). ''Converting a Swap-Based System to do Paging in an Architecture Lacking Page-Reference Bits''. Proceedings of the 8th SOSP, Operating Systems Review, Vol. 15, No. 5, pp. 78-86 | ||

* [[Bruce W. Leverett]], [http://genealogy.math.ndsu.nodak.edu/id.php?id=95738 Peter G. Hibbard] ('''1982'''). ''[http://onlinelibrary.wiley.com/doi/10.1002/spe.4380120606/abstract An Adaptive System for Dynamic Storage Allocation]''. [http://www.informatik.uni-trier.de/~ley/db/journals/spe/spe12.html#LeverettH82 Software: Practice and Experience], [http://onlinelibrary.wiley.com/doi/10.1002/spe.v12:6/issuetoc Vol. 12, No. 6], pp. 543-555 | * [[Bruce W. Leverett]], [http://genealogy.math.ndsu.nodak.edu/id.php?id=95738 Peter G. Hibbard] ('''1982'''). ''[http://onlinelibrary.wiley.com/doi/10.1002/spe.4380120606/abstract An Adaptive System for Dynamic Storage Allocation]''. [http://www.informatik.uni-trier.de/~ley/db/journals/spe/spe12.html#LeverettH82 Software: Practice and Experience], [http://onlinelibrary.wiley.com/doi/10.1002/spe.v12:6/issuetoc Vol. 12, No. 6], pp. 543-555 | ||

| Line 270: | Line 273: | ||

* [[Jos Uiterwijk]] ('''1992'''). ''Memory Efficiency in some Heuristics''. [[ICGA Journal#15_2|ICCA Journal, Vol. 15, No. 2]] | * [[Jos Uiterwijk]] ('''1992'''). ''Memory Efficiency in some Heuristics''. [[ICGA Journal#15_2|ICCA Journal, Vol. 15, No. 2]] | ||

* [[Wim Pijls]], [[Arie de Bruin]] ('''1993'''). ''SSS*-like Algorithms in Constrained Memory.'' [[ICGA Journal#16_1|ICCA Journal, Vol. 16, No. 1]] | * [[Wim Pijls]], [[Arie de Bruin]] ('''1993'''). ''SSS*-like Algorithms in Constrained Memory.'' [[ICGA Journal#16_1|ICCA Journal, Vol. 16, No. 1]] | ||

| − | * [[Hermann Kaindl]], | + | * [[Hermann Kaindl]], Gerhard Kainz, Angelika Leeb, Harald Smetana ('''1995'''). ''How to use limited memory in heuristic search''. [[Conferences#IJCAI1995|IJCAI 1995]] |

* [[Matteo Frigo]] ('''1997'''). ''The weakest reasonable memory model.'' Masters Thesis, [[Massachusetts Institute of Technology]], Department of Electrical Engineering and Computer Science, [http://supertech.csail.mit.edu/papers/frigo-ms-thesis.pdf pdf] | * [[Matteo Frigo]] ('''1997'''). ''The weakest reasonable memory model.'' Masters Thesis, [[Massachusetts Institute of Technology]], Department of Electrical Engineering and Computer Science, [http://supertech.csail.mit.edu/papers/frigo-ms-thesis.pdf pdf] | ||

* [[Dennis Breuker]] ('''1998'''). ''Memory versus Search in Games''. Ph.D. thesis, [[Maastricht University]], pdf available via [http://www.dennisbreuker.nl/thesis/index.html Dennis Breuker's page] | * [[Dennis Breuker]] ('''1998'''). ''Memory versus Search in Games''. Ph.D. thesis, [[Maastricht University]], pdf available via [http://www.dennisbreuker.nl/thesis/index.html Dennis Breuker's page] | ||

| Line 310: | Line 313: | ||

===1980 ...=== | ===1980 ...=== | ||

* [[Marvin Minsky]] ('''1980'''). ''K-Lines: A Theory of Memory''. Cognitive Science 4, 117-133, [http://csjarchive.cogsci.rpi.edu/1980v04/i02/p0117p0133/MAIN.PDF pdf] <ref>[https://en.wikipedia.org/wiki/K-line_%28artificial_intelligence%29 K-line (artificial intelligence) from Wikipedia]</ref> | * [[Marvin Minsky]] ('''1980'''). ''K-Lines: A Theory of Memory''. Cognitive Science 4, 117-133, [http://csjarchive.cogsci.rpi.edu/1980v04/i02/p0117p0133/MAIN.PDF pdf] <ref>[https://en.wikipedia.org/wiki/K-line_%28artificial_intelligence%29 K-line (artificial intelligence) from Wikipedia]</ref> | ||

| − | * [[Dennis H. Holding]], [[Robert I. Reynolds]] ('''1982'''). ''[ | + | * [[Dennis H. Holding]], [[Robert I. Reynolds]] ('''1982'''). ''[https://link.springer.com/article/10.3758/BF03197635 Recall or Evaluation of Chess Positions as Determinants of Chess Skill]''. [https://www.springer.com/journal/13421 Memory & Cognition], Vol. 10, No. 3 |

* [[A. Harry Klopf]] ('''1982'''). ''The Hedonistic Neuron: A Theory of Memory, Learning, and Intelligence''. Hemisphere Publishing Corporation, [[University of Michigan]] | * [[A. Harry Klopf]] ('''1982'''). ''The Hedonistic Neuron: A Theory of Memory, Learning, and Intelligence''. Hemisphere Publishing Corporation, [[University of Michigan]] | ||

===1990 ...=== | ===1990 ...=== | ||

| Line 352: | Line 355: | ||

'''2013''' | '''2013''' | ||

* [http://www.talkchess.com/forum/viewtopic.php?t=46968 DrMemory: memory debugger tool for Windows (and Linux)] by [[Martin Sedlak]], [[CCC]], January 22, 2013 » [[Debugging]] | * [http://www.talkchess.com/forum/viewtopic.php?t=46968 DrMemory: memory debugger tool for Windows (and Linux)] by [[Martin Sedlak]], [[CCC]], January 22, 2013 » [[Debugging]] | ||

| − | * [http://www.open-chess.org/viewtopic.php?f=5&t=2262 Multi-threaded memory access] by [[ | + | * [http://www.open-chess.org/viewtopic.php?f=5&t=2262 Multi-threaded memory access] by [[ThinkingALot]], [[Computer Chess Forums|OpenChess Forum]], February 10, 2013 » [[Thread]], [[Shared Hash Table]] |

* [http://www.talkchess.com/forum/viewtopic.php?t=47706 Hybrid Memory Cube effect on computer chess] by [[Albert Silver]], [[CCC]], April 05, 2013 <ref>[https://en.wikipedia.org/wiki/Hybrid_Memory_Cube Hybrid Memory Cube from Wikipedia]</ref> | * [http://www.talkchess.com/forum/viewtopic.php?t=47706 Hybrid Memory Cube effect on computer chess] by [[Albert Silver]], [[CCC]], April 05, 2013 <ref>[https://en.wikipedia.org/wiki/Hybrid_Memory_Cube Hybrid Memory Cube from Wikipedia]</ref> | ||

* [http://www.talkchess.com/forum/viewtopic.php?t=49388 MEM_LARGE_PAGES] by [[Alvaro Cardoso]], [[CCC]], September 18, 2013 | * [http://www.talkchess.com/forum/viewtopic.php?t=49388 MEM_LARGE_PAGES] by [[Alvaro Cardoso]], [[CCC]], September 18, 2013 | ||

| Line 384: | Line 387: | ||

==2020 ...== | ==2020 ...== | ||

* [http://www.talkchess.com/forum3/viewtopic.php?f=7&t=74751 History of Memory Wall in Computer Chess?] by [[Srdja Matovic]], [[CCC]], August 11, 2020 | * [http://www.talkchess.com/forum3/viewtopic.php?f=7&t=74751 History of Memory Wall in Computer Chess?] by [[Srdja Matovic]], [[CCC]], August 11, 2020 | ||

| + | * [http://www.talkchess.com/forum3/viewtopic.php?f=7&t=75116 Memory management and threads] by [[Chris Whittington]], [[CCC]], September 15, 2020 » [[Thread]] | ||

| + | * [http://www.talkchess.com/forum3/viewtopic.php?f=7&t=77054 PERFT transposition table funny?!] by [[Martin Bryant]], [[CCC]], April 10, 2021 » [[Perft]], [[Transposition Table]] | ||

=External Links= | =External Links= | ||

Latest revision as of 22:33, 16 May 2023

Memory is the ability to store, retain, and recall information and experiences as researched in cognitive science. Computer memory refers to physical devices used to store data and sequences of instructions (programs) on a temporary or permanent basis, typically distinguished as fast random-access memory and relatively slow data storage.

Contents

Flip-Flop

A flip-flop or latch is a one bit memory. For instance a simple relay (K1) with its contact parallel to the On-push-button S2, "remembers" whether last action was pushing S1 (reset) or S2 (set) [2] .

A RS flip-flop is a pair of cross-coupled NAND or NOR-gates, where the outputs are feed back to the inputs. A D flip-flop, the most common flip-flop, stores the input D with the rising edge (0-1 transition) of a clock.

| RS flip-flop | D flip-flop | Discrete |

|---|---|---|

| from two NOR (red == 1) [3] | from six NAND [4] | PDP-6 flip-flop [5] [6] |

N-Bit Latches

N-Bit latches are arrays of one-bit latches or flip-flops typically as wide as a connected parallel data-bus. They may be used as a registers or scratchpad RAM inside a central processing unit.

RAM

Random access memory is a fast form of computer memory and refers to the idea that any piece of data can be stored and retrieved in a constant time, regardless of its physical location and whether or not it is related to the previous piece of data.

- Random-access memory from Wikipedia

- Volatile memory from Wikipedia

- Phase-change memory from Wikipedia

- Ferroelectric RAM from Wikipedia

Static RAM

Static RAM (SRAM) is an array of latches, where each latch has a unique address, which connects the addressed latch to its data-bus, often used as CPU cache.

Dynamic RAM

Dynamic random access memory (DRAM) is a type of random access memory that stores each bit of data in a separate capacitor within an electronic circuit. Since capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically, which is the reason to call that memory dynamic. Since DRAM takes only one transistor and capacitor per bit, it is therefor used as cheap main memory part of recent computer data storage, despite its worse latency compared to SRAM.

- Dynamic random access memory from Wikipedia

- Synchronous dynamic random access memory (SDRAM)

- DDR SDRAM with Double data rate

- Interleaved memory

- SDRAM latency

- CAS latency

- Memory controller

- Memory geometry

- Hybrid Memory Cube

DRAM write at a 4 by 4 array [7]

ROM

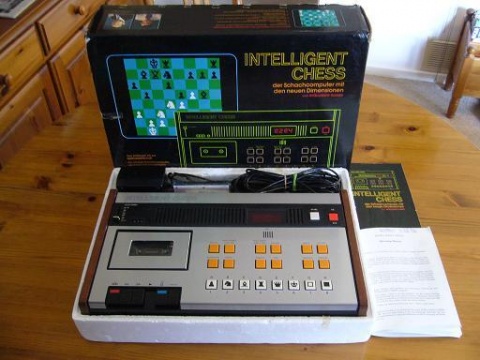

Read-only memory (ROM) is a class of storage programmed once and mainly used to distribute firmware. EPROMs have a small quartz window which admits UV light for erasure [8] . ROM or EPROM were often embedded inside a microcontroller in conjunction with some RAM. They were often used in dedicated chess computers.

National Semiconductor EPROMs 2764 and 2716 [9]

Since each data-bit stored in a ROM is a boolean function of its inputs or address, a ROM is also used to implement combinatorial logic.

Persistence

Auxiliary Storage

Beside the computer's random access main memory, auxiliary storage refer to mass storage like optical discs, and magnetic storage hard disk drives. Those devices are usually connected via a serial bus, and accessed via streams.

Compact Cassette as Auxiliary Storage in Intelligent Chess [10]

- Computer data storage from Wikipedia

- Auxiliary storage

- Mass storage

- Magnetic storage

- Magnetic tape data storage

- Floppy disk

- Hard disk drive

- RAID

- Optical discs

- Compact Disc

- DVD

- Blu-ray Disc

- Solid-state drive

- Flash memory

- USB flash drive

Historical Data Storage

- History of computing hardware from Wikipedia

- Vacuum Tube Memory from Columbia University Computing History

- Selectron tube from Wikipedia

- Williams tube from Wikipedia

- Magnetic-core memory from Wikipedia

Memory Hierarchy

Memory Management

Todays processors utilize all the above types of memory from small and fast to large but slow within the concepts of virtual memory, paging, protection and various caches.

- Memory management from Wikipedia

- Memory management unit from Wikipedia

- MSDN - Memory Management » Windows

- The Memory Management Reference Ravenbrook

- Memory protection from Wikipedia

- Memory-level parallelism (MLP) from Wikipedia

Virtual Memory

| Physical address translation [12] | Virtual and physical address space [13] |

- Virtual memory from Wikipedia

- Memory address from Wikipedia

- Physical address from Wikipedia

- Virtual address from Wikipedia

- Virtual Address eXtension (VAX) from Wikipedia

Paging

TLB

Huge Pages

Note that what Windows calls "large pages," Linux and Unix call "huge pages" or "huge TLB pages (x86 and x86-64)

- Page Size Extension from Wikipedia

- MSDN - Large-Page Support » Windows

- Huge pages part 1 Introduction by Mel Gorman, LWN.net, February 16, 2010 » Linux

- Huge pages part 2: Interfaces by Mel Gorman, LWN.net, February 24, 2010

- Huge pages part 3: Administration by Mel Gorman, LWN.net, March 3, 2010

- Huge pages part 4: benchmarking with huge pages by Mel Gorman, LWN.net, March 17, 2010

- Huge pages part 5: A deeper look at TLBs and costs by Mel Gorman, LWN.net, March 23, 2010

- Transparent huge pages in 2.6.38 by Jonathan Corbet, LWN.net, January 19, 2011

Memory Model

- Memory model (computing) from Wikipedia

- Consistency model from Wikipedia

- Memory ordering from Wikipedia

- Memory barrier from Wikipedia

- Flat memory model from Wikipedia

- Intel Memory Model from Wikipedia » Intel, x86, C, C++

- Java Memory Model from Wikipedia » Java

- Threads and memory model for C++ by Hans J. Boehm

- The Go Memory Model » Go (Programming Language)

- Shared memory from Wikipedia

- Memory model from Wikipedia

- Information on the C++11 Memory Model by Scott Meyers, April 24, 2012

- Volatile variable from Wikipedia

- Memory ordering from Wikipedia

- Memory Ordering in Modern Microprocessors, Part I by Paul E. McKenney, Linux Journal, June 30, 2005

- Memory barrier from Wikipedia

- Parallel Random Access Machine from Wikipedia

- The Shared Memory Library (SharedMemoryLib) FAQ by Márcio Serolli Pinho

- Transactional memory from Wikipedia

- Software transactional memory from Wikipedia

- Cache coherence from Wikipedia

- Distributed shared memory from Wikipedia

- Memory-mapped file from Wikipedia

- Memory disambiguation from Wikipedia

- Memory dependence prediction from Wikipedia

- OpenMP from Wikipedia

- POSIX from Wikipedia

- shm_open, The Single UNIX Specification version 2, Copyright © 1997 The Open Group

- shmget(2): allocates shared memory segment - Linux man page » Linux

- mm(3): Shared Memory Allocation - Linux man page

- CreateSharedMemory, MSDN » Windows

- Chapter 9. Boost.Interprocess - Boost 1.36.0 by Ion Gaztañaga

- Threads and memory model for C++ by Hans J. Boehm

- IPC:Shared Memory by Dave Marshall, 1999

- Symmetric Multi-Processing (SMP) from Wikipedia » SMP

- Asymmetric multiprocessing from Wikipedia

- Uniform Memory Access from Wikipedia

- Non-Uniform Memory Access (NUMA) from Wikipedia » NUMA

- Optimizing Applications for NUMA | Intel® Developer Zone

- Performance Guidelines for AMD Athlon™ 64 and AMD Opteron™ ccNUMA Multiprocessor Systems (pdf)

Cache

- Cache from Wikipedia

- Cache (computing) from Wikipedia

- Functional Principles of Cache Memory by Paul V. Bolotoff, April 2007

- CPU cache from Wikipedia

- Cache-only memory architecture (COMA) from Wikipedia

- Cache coherence from Wikipedia

- False sharing from Wikipedia

- Cache coloring from Wikipedia

- Cache hierarchy from Wikipedia

- Cache-oblivious algorithm from Wikipedia

- Cache pollution from Wikipedia

- Cache prefetching from Wikipedia

- Prefetching from Wikipedia

- assembly - The prefetch instruction - Stack Overflow

- Data Prefetch Support - GNU Project - Free Software Foundation (FSF)

- Software prefetching considered harmful by Linus Torvalds, LWN.net, May 19, 2011

- Cache replacement policies from Wikipedia

- Page cache from Wikipedia

- Acumem SlowSpotter from Wikipedia

- Analyzing Efficiency of Shared and Dedicated L2 Cache in Modern Dual-Core Processors from iXBT Labs - Computer Hardware In Detail

- Scratchpad memory from Wikipedia

Segmentation

- Memory segmentation from Wikipedia

- Data segment

- .bss

- Code segment

- Segmentation fault

- SIGSEGV

- x86 memory segmentation » x86

- Memory Limits for Applications on Windows by Steve Lionel (Intel), May 16, 2011» Windows

Allocation

Memory Footprint

Beside their individual memory footprint, chess programs have to deal with huge memory areas of transposition table and possibly caches for endgame table- or bitbases and their relative huge random access latencies.

- Memory footprint from Wikipedia

- Method and apparatus for establishing a cache footprint for shared processor logical partitions

- Memory timings from Wikipedia

- Access time

- CAS latency

- Memory bandwidth

- Bandwidth: a memory bandwidth benchmark for x86 / x86_64 based Linux/Windows/MacOSX by Zack Smith

- Cache pollution

- Thrashing (computer science)

- False sharing from Wikipedia

- Miles Davis Quintet - Footprints (Wayne Shorter), New York, 1966, YouTube Video

- Monika Malczak Quartet - Footprints, Witold Lutosławski Concert Studio of Polish Radio, Warsaw, May 20, 2016, YouTube Video

Multiprocessing

Memory versus Search

- Best-First

- Depth-First

- Endgame Tablebases

- Knowledge

- Learning

- MTD(f)

- Parallel Search

- Persistent Hash Table

- Space-Time Tradeoff

- SSS* and Dual*

- Transposition Table

See also

- Algorithms

- Array

- Cognition

- Combinatorial Logic

- Data

- Hash Table

- Psychology

- Queue

- Sequential Logic

- Shared Hash Table

- Stack

Publications

Computer Memory

1960 ...

- Kenneth C. Knowlton (1965). A Fast storage allocator. Communications of the ACM, Vol. 8, No. 10 : 623-625

1970 ...

- Paul W. Purdom, Stephen M. Stigler (1970). Statistical Properties of the Buddy System. Journal of the ACM, Vol. 17, No. 4 [14]

- Donald Eastlake (1977). Tertiary Memory Access and Performance in the Datacomputer. VLDB 1977

1980 ...

- Paul W. Purdom, Cynthia A. Brown (1980). Exact formulas for the buddy system. Information Sciences, Vol. 22, No. 1

- Ozalp Babaoglu, William Joy (1981). Converting a Swap-Based System to do Paging in an Architecture Lacking Page-Reference Bits. Proceedings of the 8th SOSP, Operating Systems Review, Vol. 15, No. 5, pp. 78-86

- Bruce W. Leverett, Peter G. Hibbard (1982). An Adaptive System for Dynamic Storage Allocation. Software: Practice and Experience, Vol. 12, No. 6, pp. 543-555

- Subir Bhattacharya, Amitava Bagchi (1986). Making Best Use of Available Memory when Searching Game Trees. Proceedings of the 5th International Conference on Artificial Intelligence (AAAI-86), pp. 163-167. AAAI/MIT Press, Boston, MA.

1990 ...

- Peter W. Frey (1991). Memory-Based Expertise: Computer Chess vs. AI. ICCA Journal, Vol. 14, No. 4

- Jos Uiterwijk (1992). Memory Efficiency in some Heuristics. ICCA Journal, Vol. 15, No. 2

- Wim Pijls, Arie de Bruin (1993). SSS*-like Algorithms in Constrained Memory. ICCA Journal, Vol. 16, No. 1

- Hermann Kaindl, Gerhard Kainz, Angelika Leeb, Harald Smetana (1995). How to use limited memory in heuristic search. IJCAI 1995

- Matteo Frigo (1997). The weakest reasonable memory model. Masters Thesis, Massachusetts Institute of Technology, Department of Electrical Engineering and Computer Science, pdf

- Dennis Breuker (1998). Memory versus Search in Games. Ph.D. thesis, Maastricht University, pdf available via Dennis Breuker's page

- Harald Prokop (1999). Cache-Oblivious Algorithms. Masters thesis, Department of Electrical Engineering and Computer Science, MIT, pdf [15]

- Erik D. Demaine, J. Ian Munro (1999). Fast Allocation and Deallocation with an Improved Buddy System. FSTTCS 1999, Lecture Notes in Computer Science, Vol. 1738, Springer [16]

2000 ...

- Yue Yang, Ganesh Gopalakrishnan, Gary Lindstrom (2002). Specifying Java Thread Semantics Using a Uniform Memory Model. Java Grande 2002, pdf

- F. Warren Burton, David J. Simpson (2000). Memory requirements for parallel programs. Parallel Computing, Vol. 26, Nos. 13-14

- Qiang Wu, Artem Pyatakov, Alexey Spiridonov, Easwaran Raman, Douglas W. Clark, David I. August (2004). Exposing Memory Access Regularities Using Object-Relative Memory Profiling. CGO 2004, pdf

- Ulrich Drepper (2007). What Every Programmer Should Know About Memory. pdf, also hosted by LWN.net

- Memory part 1

- Memory part 2: CPU caches

- Memory part 3: Virtual Memory

- Memory part 4: NUMA support

- Memory part 5: What programmers can do

- David Gay, Robert Ennals, Eric Brewer (2007). Safe manual memory management. ISMM 2007

- David Silver, Richard Sutton, Martin Müller (2008). Sample-Based Learning and Search with Permanent and Transient Memories. In Proceedings of the 25th International Conference on Machine Learning, pdf

2010 ...

- Aaron Becker, Gengbin Zheng, Laxmikant Kale (2011). Distributed Memory Load Balancing. Encyclopedia of Parallel Computing, Springer

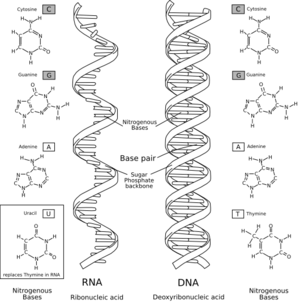

- George Church, Yuan Gao, Sriram Kosuri (2012). Next-Generation Digital Information Storage in DNA. Science [17] [18]

- Matteo Frigo, Charles Leiserson, Harald Prokop, Sridhar Ramachandran (2012). Cache-Oblivious Algorithms. ACM Transactions on Algorithms, Vol. 8, No. 1, pdf

- Aravinthan Athmanathan, Milos Stanisavljevic, Junho Cheon, Seokjoon Kang, Changyong Ahn, Junghyuk Yoon, Min-Chul Shin, Taekseung Kim, Nikolaos Papandreou, Haralampos Pozidis, Evangelos Eleftheriou (2014). A 6-bit drift-resilient readout scheme for multi-level Phase-Change Memory. A-SSCC 2014

- Milos Stanisavljevic, Aravinthan Athmanathan, Nikolaos Papandreou, Haralampos Pozidis, Evangelos Eleftheriou (2015). Phase-change memory: Feasibility of reliable multilevel-cell storage and retention at elevated temperatures. IRPS 2015

- Aravinthan Athmanathan, Milos Stanisavljevic, Nikolaos Papandreou, Haralampos Pozidis, Evangelos Eleftheriou (2016). Multilevel-Cell Phase-Change Memory: A Viable Technology. IEEE Journal of Emerging and Selected Topics in Circuits and Systems, Vol. 6, No. 1

- Sylvain Gelly, Karol Kurach, Marcin Michalski, Xiaohua Zhai (2018). MemGEN: Memory is All You Need. arXiv:1803.11203 [19]

- Milos Stanisavljevic, Thomas Mittelholzer, Nikolaos Papandreou, Thomas P. Parnell, Haralampos Pozidis (2018). Drift-Invariant Detection for Multilevel Phase-Change Memory. ISCAS 2018

Cognition

1960 ...

- Adriaan de Groot (1966). Perception and Memory versus Thought: Some Old Ideas and Recent Findings. Problem Solving: Research, Method, and Theory (ed. B. Kleinmuntz), pp. 19-50. John Wiley, New York.

1970 ...

- Herbert Simon, Kevin J. Gilmartin (1973). A Simulation of Memory for Chess Positions. Cognitive Psychology, Vol. 5, pp. 29-46. pdf » MAPP

- Peter W. Frey, Peter Adesman (1976). Recall Memory for Visually Presented Chess Positions. Memory & Cognition, Vol. 4, No. 5, 541-547

- Neil Charness (1976). Memory for Chess Positions: Resistance to Interference. Journal of Experimental Psychology: Human Learning and Memory, Vol. 2, No. 6, pp. 641-653 » MAPP

- Judith S. Reitman (1976). Mechanisms of Forgetting in Short-term Memory. Cognitive Psychology, Vol. 2, No. 2

- Judith S. Reitman (1976). Skilled Perception in Go: Deducing Memory Structures from Inter-Response Times. Cognitive Psychology, Vol. 8, No, 3

- Sarah E. Goldin (1978). Memory for the ordinary: Typicality effects in chess memory. Journal of Experimental Psychology: Human Learning and Memory, Vol. 4, No. 6, pp. 605-616

- Sarah E. Goldin (1979). Recognition memory for chess positions: Some preliminary research. American Journal of Psychology, Vol 92, No. 1, pp. 19-32

1980 ...

- Marvin Minsky (1980). K-Lines: A Theory of Memory. Cognitive Science 4, 117-133, pdf [20]

- Dennis H. Holding, Robert I. Reynolds (1982). Recall or Evaluation of Chess Positions as Determinants of Chess Skill. Memory & Cognition, Vol. 10, No. 3

- A. Harry Klopf (1982). The Hedonistic Neuron: A Theory of Memory, Learning, and Intelligence. Hemisphere Publishing Corporation, University of Michigan

1990 ...

- Fernand Gobet (1993). A Computer Model of Chess Memory. Proceedings of the 15th Annual Meeting of the Cognitive Science Society, pp. 463-468.

- Fernand Gobet, Peter Jansen (1994). Towards a chess program based on a model of human memory. Advances in Computer Chess 7. abstract

- Robert W. Howard (1995). Learning and Memory: Major Ideas, Principles, Issues and Applications. Praeger, amazon.com

- Adriaan de Groot, Fernand Gobet (1996). Perception and memory in chess. Heuristics of the professional eye. Assen: Van Gorcum, The Netherlands. ISBN 90-232-2949-5. Chapter 9; A discussion: Two authors, two different views? word reprint

- Fernand Gobet, Herbert Simon (1996). Templates in Chess Memory: A Mechanism for Recalling Several Boards. Cognitive Psychology, Vol. 31, pp. 1-40.

- Fernand Gobet, Herbert Simon (1996). Recall of random and distorted positions: Implications for the theory of expertise. Memory & Cognition, 24, 493-503.

- Fernand Gobet, Herbert Simon (1996). Recall of rapidly presented random chess positions is a function of skill. Psychonomic Bulletin & Review, 3, 159-163, word reprint

- Fernand Gobet, Herbert Simon (1998). Expert chess memory: Revisiting the chunking hypothesis. Memory, 6, 225-255

- Richard S. Schultetus, Neil Charness (1999). Recall vs. position evaluation revisited: The importance of position-specific memory in chess skill. American Journal of Psychology, Vol. 112, No. 4, 555-569.

2000 ...

- Pertti Saariluoma, Tei Laine (2001). Novice construction of chess memory. Scandinavian Journal of Psychology, Vol. 42, No. 2 [21]

- Dharshan Kumaran, Eleanor A. Maguire (2005). The Human Hippocampus: Cognitive Maps or Relational Memory? Journal of Neuroscience, Vol. 25, No. 31

- Guillermo Campitelli, Fernand Gobet, Amanda Parker (2005). Structure and Stimulus Familiarity: A Study of Memory in Chess-Players with Functional Magnetic Resonance Imaging. The Spanish Journal of Psychology Vol. 8, No. 2, 238-245. pdf

- Alan H. Bond (2005). Representing episodic memory in a system-level model of the brain. Neurocomputing, vol 65-66, pp. 261-273, pdf

- Guillermo Campitelli, Fernand Gobet, Kay Head, Mark Buckley, Amanda Parker (2007). Brain localisation of memory chunks in chessplayers. International Journal of Neuroscience, 117

- Dharshan Kumaran (2008). Short-Term Memory and The Human Hippocampus. Journal of Neuroscience, Vol. 28, No. 15, pdf

- Demis Hassabis (2009). The Neural Processes Underpinning Episodic Memory. Ph.D. thesis, University College London, Supervisor Eleanor A. Maguire, pdf

Forum Posts

1995 ...

- cache sizes by Tom Kerrigan, rgcc, August 12, 1997

2000 ...

- Difference in chess between DDR and PC133 SDRAM? by Javier Ros Padilla, CCC, April 16, 2003

- Another memory latency test by Dieter Bürßner, CCC, July 17, 2003

- Re: Static memory allocation by Matt Taylor, comp.lang.asm.x86, July 03, 2004

2005 ...

- Minimizing Sharing of Data between Physical Processors by Pradu Kannan, CCC, May 19, 2008

- malloc more than 2GB ? by Frank Phillips, CCC, March 28, 2009

- Cache pollution when reading/writing hash table by Marco Costalba, CCC, August 09, 2009

- Questions on volatile keyword and memory barriers by Pradu Kannan, CCC, August 16, 2009

2010 ...

- Is a querying the hash tables such a huge bottleneck? by Oliver Uwira, CCC, October 28, 2010

2011

- MSVC calloc question by Harm Geert Muller, CCC, March 17, 2011

2012

- Memory question by Fermin Serrano, CCC, May 19, 2012

- DNA data storage breaks records by Terry McCracken, CCC, August 18, 2012 [22]

2013

- DrMemory: memory debugger tool for Windows (and Linux) by Martin Sedlak, CCC, January 22, 2013 » Debugging

- Multi-threaded memory access by ThinkingALot, OpenChess Forum, February 10, 2013 » Thread, Shared Hash Table

- Hybrid Memory Cube effect on computer chess by Albert Silver, CCC, April 05, 2013 [23]

- MEM_LARGE_PAGES by Alvaro Cardoso, CCC, September 18, 2013

- Multithreaded LRU by Alvaro Cardoso, CCC, October 06, 2013 » Endgame Tablebases

- tablebase caching / mmap() / page cache by Ronald de Man, CCC, October 13, 2013 » Endgame Tablebases, Syzygy Bases

- Table Base Cache Size question by Rob Nicholas, CCC, December 05, 2013 » Endgame Tablebases

2014

- Intel i3 L2 cache by Harm Geert Muller, CCC, January 28, 2014 » x86-64 [24]

- c++11 std::atomic and memory_order_relaxed by Kevin Hearn, CCC, April 01, 2014 » C++

- Speculative prefetch by Peter Österlund, CCC, September 27, 2014 » Transposition Table

- Tablebase access using a Solid State Disk by Steven Edwards, CCC, October 16, 2014 » Endgame Tablebases

- USB 3 Storage for Syzygy WDL files by Louis Zulli, CCC, December 13, 2014 » Syzygy Bases, USB 3.0

2015 ...

- Low-RAM engine by Harm Geert Muller, CCC, January 28, 2015

- The effect of dual channel RAM by Volker Annuss, CCC, March 01, 2015 » Arminius

- One hundred thirty gigabytes by Steven Edwards, CCC, July 03, 2015

- 3D XPoint by Edmund Moshammer, CCC, August 02, 2015 [25]

- Hash cache by Harm Geert Muller, CCC, October 12, 2015 » Hash Table, Transposition Table

2016

- NUMA 101 by Robert Hyatt, CCC, January 07, 2016 » Parallel Search

- NUMA in a YBWC implementation by Edsel Apostol, CCC, July 20, 2016 » Young Brothers Wait Concept

- lets get the ball moving down the field on numa awareness by Mohammed Li, FishCooking, August 30, 2016 » NUMA, Stockfish, asmFish

- Tipical cache and branch misses for a chess engine by Nicu Ionita, CCC, September 14, 2016 » Avoiding Branches, Profiling

- What do you do with NUMA? by Matthew Lai, CCC, September 19, 2016 » NUMA

- L3 cache, RAM and other performance factors by Nimzy, Rybka Forum, December 04, 2016 » Playing Strength

2017 ...

- 6-men Syzygy from HDD and USB 3.0 by Kai Laskos, CCC, April 04, 2017 » Komodo, Playing Strength, Syzygy Bases, USB 3.0

- RAM speed and engine strength by John Hartmann, CCC, May 03, 2017 » RAM, Playing Strength

- Probing tablebases through USB 3.0 by Jon Fredrik Åsvang, CCC, September 25, 2017 » Syzygy Bases, USB 3.0

- Prefetch and Threading by Dennis Sceviour, CCC, April 25, 2019 » Thread, Transposition Table

2020 ...

- History of Memory Wall in Computer Chess? by Srdja Matovic, CCC, August 11, 2020

- Memory management and threads by Chris Whittington, CCC, September 15, 2020 » Thread

- PERFT transposition table funny?! by Martin Bryant, CCC, April 10, 2021 » Perft, Transposition Table

External Links

Computer Memory

- Bits by Lawrence J. Krakauer

- Computer memory from Wikipedia

- Data dictionary from Wikipedia

- Lookup table from Wikipedia

- Moby Memory by Lawrence J. Krakauer » PDP-6

- Multi-level cell from Wikipedia

- Semiconductor memory from Wikipedia

- Universal memory from Wikipedia

- Von Neumann architecture from Wikipedia

Gustavo Duarte's Blog

from Best Of by Gustavo Duarte:

- Motherboard Chipsets and the Memory Map

- Anatomy of a Program in Memory

- How The Kernel Manages Your Memory

- Page Cache, the Affair Between Memory and Files

- Memory Translation and Segmentation

- Getting Physical With Memory

- CPU Rings, Privilege, and Protection

- Cache: a place for concealment and safekeeping

- The Thing King

Cognition

- Cognition from Wikipedia

- Cognitive Psychology and Cognitive Neuroscience/Memory from Wikibooks

- Long-term memory from Wikipedia

- Memory from Wikipedia

- Recall (memory) from Wikipedia

- Short-term memory from Wikipedia

- Working memory from Wikipedia

Neuroscience

- Neuroscience from Wikipedia

- Biological neural network from Wikipedia

- Brain from Wikipedia

- Cognitive neuroscience from Wikipedia

- Computation, Memory, Nature, and Life - Is digital storage the secret of life? by John Walker

- Human brain from Wikipedia

- Memory (biological) from Wikiversity

Misc

- Art of memory from Wikipedia

- Electric Fence (Memory Debugger) from Wikipedia » Debugging

- Mnemonic from Wikipedia

- Moore's law from Wikipedia

- Paper data storage from Wikipedia

- Al Di Meola, Stanley Clarke, Jean-Luc Ponty - Memory Canyon, Montreux 1994, YouTube Video

References

- ↑ Data storage device from Wikipedia

- ↑ Selbsthaltefunktion from Wikidepia.de (German)

- ↑ Latch (electronics) from Wikipedia

- ↑ Flip-flop (electronics) from Wikipedia

- ↑ Bits by Lawrence J. Krakauer

- ↑ PDP-6 Circuit Instruction Manual, © 1966, Digital Equipment Corporation (pdf)

- ↑ Dynamic random access memory from Wikipedia

- ↑ How to program a 2716

- ↑ Category:EPROM 2716 - Wikimedia Commons

- ↑ Intelligent Chess from Chess Computer UK by Mike Watters

- ↑ 3D XPoint by Edmund Moshammer, CCC, August 02, 2015

- ↑ Page table from Wikipedia

- ↑ Virtual address from Wikipedia

- ↑ Buddy memory allocation from Wikipedia

- ↑ Cache-oblivious algorithm from Wikipedia

- ↑ Buddy memory allocation from Wikipedia

- ↑ DNA data storage breaks records : Nature News & Comment by Monya Baker, August 16, 2012

- ↑ DNA data storage breaks records by Terry McCracken, CCC, August 18, 2012

- ↑ April 01, 2018

- ↑ K-line (artificial intelligence) from Wikipedia

- ↑ Fernand Gobet (2007). Chunk hierarchies and retrieval structures: Comments on Saariluoma and Laine. Scandinavian Journal of Psychology, 42. pdf

- ↑ George Church, Yuan Gao, Sriram Kosuri (2012). Next-Generation Digital Information Storage in DNA. Science

- ↑ Hybrid Memory Cube from Wikipedia

- ↑ Intel Nehalem Core i3

- ↑ 3D XPoint from Wikipedia