Difference between revisions of "General Setwise Operations"

GerdIsenberg (talk | contribs) (Created page with "'''Home * Board Representation * Bitboards * General Setwise Operations''' FILE:Upward by Vasily Kandinsky, 1929.jpg|border|right|thumb| |[[Arts#Kandi...") |

GerdIsenberg (talk | contribs) |

||

| (14 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

'''[[Main Page|Home]] * [[Board Representation]] * [[Bitboards]] * General Setwise Operations''' | '''[[Main Page|Home]] * [[Board Representation]] * [[Bitboards]] * General Setwise Operations''' | ||

| − | [[FILE:Upward by Vasily Kandinsky, 1929.jpg|border|right|thumb | + | [[FILE:Upward by Vasily Kandinsky, 1929.jpg|border|right|thumb|[[:Category:Wassily Kandinsky|Wassily Kandinsky]] - Upward, 1929 <ref>[[:Category:Wassily Kandinsky|Wassily Kandinsky]] - Upward, 1929, [https://en.wikipedia.org/wiki/Peggy_Guggenheim_Collection Peggy Guggenheim Collection], [https://en.wikipedia.org/wiki/Wikimedia_Commons Wikimedia COmmons]</ref> ]] |

| − | |[[ | ||

'''General Setwise Operations''',<br/> | '''General Setwise Operations''',<br/> | ||

| Line 19: | Line 18: | ||

if (a != b) -> both sets are not equal | if (a != b) -> both sets are not equal | ||

</pre> | </pre> | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86]] has a cmp-instruction, which internally performs a subtraction to set its internal processor flags (carry, zero, overflow) accordantly, for instance the zero-flag if both sets are equal. Those flags are then used by conditional jump or move instructions. | [[x86]] has a cmp-instruction, which internally performs a subtraction to set its internal processor flags (carry, zero, overflow) accordantly, for instance the zero-flag if both sets are equal. Those flags are then used by conditional jump or move instructions. | ||

<pre> | <pre> | ||

| Line 42: | Line 41: | ||

set-wise = {a1, b1, c1, d1, ....., e8, f8, g8, h8} | set-wise = {a1, b1, c1, d1, ....., e8, f8, g8, h8} | ||

</pre> | </pre> | ||

| − | as [https://en.wikipedia.org/wiki/Venn_diagram Venn | + | as bitboard diagrams and [https://en.wikipedia.org/wiki/Venn_diagram Venn diagrams] |

| − | + | [[FILE:Venn0000.svg|border|right|thumb|240px|Empty]] | |

| − | + | <pre> | |

| − | + | Empty Universe | |

| − | + | . . . . . . . . 1 1 1 1 1 1 1 1 | |

| − | + | . . . . . . . . 1 1 1 1 1 1 1 1 | |

| − | + | . . . . . . . . 1 1 1 1 1 1 1 1 | |

| − | <pre> | + | . . . . . . . . 1 1 1 1 1 1 1 1 |

| − | Empty | + | . . . . . . . . 1 1 1 1 1 1 1 1 |

| − | . . . . . . . . | + | . . . . . . . . 1 1 1 1 1 1 1 1 |

| − | . . . . . . . . | + | . . . . . . . . 1 1 1 1 1 1 1 1 |

| − | . . . . . . . . | + | . . . . . . . . 1 1 1 1 1 1 1 1 |

| − | . . . . . . . . | ||

| − | . . . . . . . . | ||

| − | . . . . . . . . | ||

| − | . . . . . . . . | ||

| − | . . . . . . . . | ||

</pre> | </pre> | ||

| − | + | [[FILE:Venn1111.svg|border|right|thumb|240px|Universe]] | |

Programmers often wonder to use -1 in [[C]], [[Cpp|C++]] as unsigned constant. See [[General Setwise Operations#TheTwosComplement|The Two's Complement]] - alternately one may use ~0 to define the universal set. Since in [[C]] or [[Cpp|C++]], decimal numbers without ULL suffix are treated as 32-bit integers, constants outside the integer range need some care concerning sign or zero extension. Const declarations or using the [[Bitboards#DefiningBitboards|C64 Macro]] is recommended: | Programmers often wonder to use -1 in [[C]], [[Cpp|C++]] as unsigned constant. See [[General Setwise Operations#TheTwosComplement|The Two's Complement]] - alternately one may use ~0 to define the universal set. Since in [[C]] or [[Cpp|C++]], decimal numbers without ULL suffix are treated as 32-bit integers, constants outside the integer range need some care concerning sign or zero extension. Const declarations or using the [[Bitboards#DefiningBitboards|C64 Macro]] is recommended: | ||

<pre> | <pre> | ||

| Line 85: | Line 79: | ||

<span id="Intersection"></span> | <span id="Intersection"></span> | ||

==Intersection== | ==Intersection== | ||

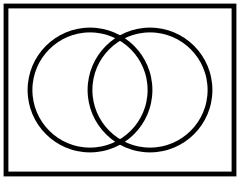

| − | [[FILE:Venn0001.svg| | + | [[FILE:Venn0001.svg|border|right|thumb|240px|Intersection]] |

In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Intersection_%28set_theory%29 intersection] is denoted as: | In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Intersection_%28set_theory%29 intersection] is denoted as: | ||

| − | A ∩ B | + | <span style="font-size: 140%;">A ∩ B</span> |

In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Logical_conjunction conjunction] is denoted as: | In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Logical_conjunction conjunction] is denoted as: | ||

| − | a ∧ b | + | <span style="font-size: 140%;">a ∧ b</span> |

Bitboard intersection or conjunction is performed by [https://en.wikipedia.org/wiki/Bitwise_operation#AND bitwise and] (binary operator & in [[C]], [[Cpp|C++]] or [[Java]], and the keyword "AND" in [[Pascal]]). | Bitboard intersection or conjunction is performed by [https://en.wikipedia.org/wiki/Bitwise_operation#AND bitwise and] (binary operator & in [[C]], [[Cpp|C++]] or [[Java]], and the keyword "AND" in [[Pascal]]). | ||

intersection = a & b | intersection = a & b | ||

| − | '''Truth Table''' | + | '''Truth Table'''<br/> |

Truth table of [https://en.wikipedia.org/wiki/AND_gate and] for one bit, for a '1' result both inputs need to be '1': | Truth table of [https://en.wikipedia.org/wiki/AND_gate and] for one bit, for a '1' result both inputs need to be '1': | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 122: | Line 116: | ||

Conjunction acts like a bitwise minimum, min(a, b) or as bitwise multiplication (a * b). | Conjunction acts like a bitwise minimum, min(a, b) or as bitwise multiplication (a * b). | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise and: | [[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise and: | ||

<pre> | <pre> | ||

| Line 132: | Line 126: | ||

vpand ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 & ymm2 | vpand ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 & ymm2 | ||

</pre> | </pre> | ||

| − | [[SSE2]]-intrinsic [ | + | [[SSE2]]-intrinsic [[SSE2#_mm_and_si128|_mm_and_si128]]<br/> |

| − | [[AVX2]]-intrinsic [ | + | [[AVX2]]-intrinsic [[AVX2#_mm256_and_si256|_mm256_and_si256]]<br/> |

[[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | ||

| − | '''Idempotent''' | + | '''Idempotent''' <br/> |

Conjunction is [https://en.wikipedia.org/wiki/Idempotence idempotent]. | Conjunction is [https://en.wikipedia.org/wiki/Idempotence idempotent]. | ||

a & a == a | a & a == a | ||

| − | '''Commutative''' | + | '''Commutative''' <br/> |

Conjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | Conjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | ||

a & b == b & a | a & b == b & a | ||

| − | '''Associative''' | + | '''Associative'''<br/> |

Conjunction is [https://en.wikipedia.org/wiki/Associative associative]. | Conjunction is [https://en.wikipedia.org/wiki/Associative associative]. | ||

(a & b) & c == a & (b & c) | (a & b) & c == a & (b & c) | ||

| − | '''Subset''' | + | '''Subset''' <br/> |

The intersection of two sets is [https://en.wikipedia.org/wiki/Subset subset] of both. | The intersection of two sets is [https://en.wikipedia.org/wiki/Subset subset] of both. | ||

| Line 165: | Line 159: | ||

</pre> | </pre> | ||

<span id="DisjointSets"></span> | <span id="DisjointSets"></span> | ||

| − | '''Disjoint Sets''' | + | '''Disjoint Sets''' <br/> |

To test whether two sets are [https://en.wikipedia.org/wiki/Disjoint disjoint] - that is their intersection is empty - compiler emit the [[x86]] test-instruction instead of and. That saves the content of a register, if the intersection is not otherwise needed: | To test whether two sets are [https://en.wikipedia.org/wiki/Disjoint disjoint] - that is their intersection is empty - compiler emit the [[x86]] test-instruction instead of and. That saves the content of a register, if the intersection is not otherwise needed: | ||

<pre> | <pre> | ||

| Line 173: | Line 167: | ||

<span id="Union"></span> | <span id="Union"></span> | ||

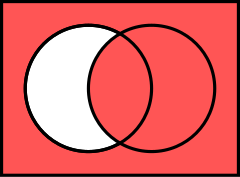

==Union== | ==Union== | ||

| − | [[FILE:Venn0111.svg| | + | [[FILE:Venn0111.svg|border|right|thumb|240px|Union]] |

| − | |||

In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Union_%28set_theory%29 union] is denoted as: | In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Union_%28set_theory%29 union] is denoted as: | ||

| − | A ∪ B | + | <span style="font-size: 140%;">A ∪ B</span> |

In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Logical_disjunction disjunction] is denoted as: | In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Logical_disjunction disjunction] is denoted as: | ||

| − | a ∨ b | + | <span style="font-size: 140%;">a ∨ b</span> |

The union or disjunction of two bitboards is applied by [https://en.wikipedia.org/wiki/Bitwise_operation#OR bitwise or] (binary operator | in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "OR" in [[Pascal]]). The union is superset of the [[General Setwise Operations#Intersection|intersection]], while the [[General Setwise Operations#Intersection|intersection]] is [https://en.wikipedia.org/wiki/Subset subset] of the union. | The union or disjunction of two bitboards is applied by [https://en.wikipedia.org/wiki/Bitwise_operation#OR bitwise or] (binary operator | in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "OR" in [[Pascal]]). The union is superset of the [[General Setwise Operations#Intersection|intersection]], while the [[General Setwise Operations#Intersection|intersection]] is [https://en.wikipedia.org/wiki/Subset subset] of the union. | ||

union = a | b | union = a | b | ||

| − | '''Truth Table''' | + | '''Truth Table''' <br/> |

Truth table of [https://en.wikipedia.org/wiki/OR_gate or] for one bit, one set input bits is sufficient to set the output: | Truth table of [https://en.wikipedia.org/wiki/OR_gate or] for one bit, one set input bits is sufficient to set the output: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 207: | Line 200: | ||

Disjunction acts like bitwise maximum, max(a, b) or as addition with saturation, min(a + b, 1). It can also be interpreted as sum minus product, a + b - a*b, with possible temporary overflow of one binary digit to two - or with modulo 2 arithmetic. | Disjunction acts like bitwise maximum, max(a, b) or as addition with saturation, min(a + b, 1). It can also be interpreted as sum minus product, a + b - a*b, with possible temporary overflow of one binary digit to two - or with modulo 2 arithmetic. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise or: | [[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise or: | ||

<pre> | <pre> | ||

| Line 216: | Line 209: | ||

vpor ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 | ymm2 | vpor ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 | ymm2 | ||

</pre> | </pre> | ||

| − | [[SSE2]]-intrinsic [ | + | [[SSE2]]-intrinsic [[SSE2#_mm_or_si128|_mm_or_si128]]<br/> |

| − | [[AVX2]]-intrinsic [ | + | [[AVX2]]-intrinsic [[AVX2#_mm256_or_si256|_mm256_or_si256]]<br/> |

| − | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | + | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]]<br/> |

| − | '''Idempotent''' | + | '''Idempotent''' <br/> |

Disjunction is [https://en.wikipedia.org/wiki/Idempotence idempotent]. | Disjunction is [https://en.wikipedia.org/wiki/Idempotence idempotent]. | ||

a | a == a | a | a == a | ||

| − | '''Commutative''' | + | '''Commutative''' <br/> |

Disjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | Disjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | ||

a | b == b | a | a | b == b | a | ||

| − | '''Associative''' | + | '''Associative''' <br/> |

Disjunction is [https://en.wikipedia.org/wiki/Associative associative]. | Disjunction is [https://en.wikipedia.org/wiki/Associative associative]. | ||

(a | b) | c == a | (b | c) | (a | b) | c == a | (b | c) | ||

<span id="DistributiveAndOr"></span> | <span id="DistributiveAndOr"></span> | ||

| − | '''Distributive''' | + | '''Distributive''' <br/> |

Disjunction is [https://en.wikipedia.org/wiki/Distributivity distributive] over [[General Setwise Operations#Intersection|conjunction]] and vice versa: | Disjunction is [https://en.wikipedia.org/wiki/Distributivity distributive] over [[General Setwise Operations#Intersection|conjunction]] and vice versa: | ||

x | (y & z) == (x | y) & (x | z) | x | (y & z) == (x | y) & (x | z) | ||

x & (y | z) == (x & y) | (x & z) | x & (y | z) == (x & y) | (x & z) | ||

| − | '''Superset''' | + | '''Superset''' <br/> |

The union of two sets is superset of both. For instance the union of all white and black pieces are the set of all occupied squares: | The union of two sets is superset of both. For instance the union of all white and black pieces are the set of all occupied squares: | ||

<pre> | <pre> | ||

| Line 250: | Line 243: | ||

<span id="ComplementSet"></span> | <span id="ComplementSet"></span> | ||

==Complement Set== | ==Complement Set== | ||

| − | [[FILE:Venn1010.svg| | + | [[FILE:Venn1010.svg|border|right|thumb|240px|Complement]] |

In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Complement_%28set_theory%29 complement set] is denoted as: | In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Complement_%28set_theory%29 complement set] is denoted as: | ||

| − | A<span style="vertical-align: super;">∁</span> | + | <span style="font-size: 140%;">A</span><span style="vertical-align: super;">∁</span> |

In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Negation negation] is denoted as: | In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Negation negation] is denoted as: | ||

| − | ¬a | + | <span style="font-size: 140%;">¬a</span> |

The complement set (absolute complement set), negation or [https://en.wikipedia.org/wiki/Ones%27_complement#Ones.27_complement ones' complement] has it's equivalent in [https://en.wikipedia.org/wiki/Bitwise_operation#NOT bitwise not] (unary operator '~' in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "NOT" in [[Pascal]]). | The complement set (absolute complement set), negation or [https://en.wikipedia.org/wiki/Ones%27_complement#Ones.27_complement ones' complement] has it's equivalent in [https://en.wikipedia.org/wiki/Bitwise_operation#NOT bitwise not] (unary operator '~' in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "NOT" in [[Pascal]]). | ||

| − | '''Truth Table''' | + | '''Truth Table''' <br/> |

Truth table of [https://en.wikipedia.org/wiki/NOT_gate not] for one bit: | Truth table of [https://en.wikipedia.org/wiki/NOT_gate not] for one bit: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 272: | Line 265: | ||

The complement can be interpreted as bitwise subtraction (1 - a). | The complement can be interpreted as bitwise subtraction (1 - a). | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

Available as general purpose instruction. | Available as general purpose instruction. | ||

| − | + | not rax ; rax = ~rax | |

| − | not rax ; rax = ~rax | ||

| − | |||

[[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | ||

| − | '''Empty Squares''' | + | '''Empty Squares'''<br/> |

The set of empty squares for instance is the complement-set of all occupied squares and vice versa: | The set of empty squares for instance is the complement-set of all occupied squares and vice versa: | ||

<pre> | <pre> | ||

| Line 299: | Line 290: | ||

!-1 == 0 | !-1 == 0 | ||

<span id="Complementlaws"></span> | <span id="Complementlaws"></span> | ||

| − | '''Complement laws''' | + | '''Complement laws'''<br/> |

* The [[General Setwise Operations#Union|union]] of a set with it's complement is the universal set -1. | * The [[General Setwise Operations#Union|union]] of a set with it's complement is the universal set -1. | ||

* The [[General Setwise Operations#Intersection|intersection]] of a set with it's complement is the empty set 0 - both are [https://en.wikipedia.org/wiki/Disjoint disjoint]. | * The [[General Setwise Operations#Intersection|intersection]] of a set with it's complement is the empty set 0 - both are [https://en.wikipedia.org/wiki/Disjoint disjoint]. | ||

| Line 308: | Line 299: | ||

~(-1) == 0 | ~(-1) == 0 | ||

<span id="DeMorganslaws"></span> | <span id="DeMorganslaws"></span> | ||

| − | '''De Morgan's laws''' | + | '''De Morgan's laws''' <br/> |

* Complement of [[General Setwise Operations#Union|union]] ([https://en.wikipedia.org/wiki/NOR_gate NOR] ) is the [[General Setwise Operations#Intersection|intersection]] of the complements <ref>[[Mathematician#ADeMorgan|Augustus De Morgan]] ('''1860'''). ''[http://books.google.com/books?id=Od3jgF5rZtgC Syllabus of a Proposed System of Logic]''. Walton & Malbery</ref>. | * Complement of [[General Setwise Operations#Union|union]] ([https://en.wikipedia.org/wiki/NOR_gate NOR] ) is the [[General Setwise Operations#Intersection|intersection]] of the complements <ref>[[Mathematician#ADeMorgan|Augustus De Morgan]] ('''1860'''). ''[http://books.google.com/books?id=Od3jgF5rZtgC Syllabus of a Proposed System of Logic]''. Walton & Malbery</ref>. | ||

* Complement of [[General Setwise Operations#Intersection|intersection]] ([https://en.wikipedia.org/wiki/NAND_logic NAND] or [https://en.wikipedia.org/wiki/Sheffer_stroke Sheffer stroke] ) is the [[General Setwise Operations#Union|union]] of the complements. | * Complement of [[General Setwise Operations#Intersection|intersection]] ([https://en.wikipedia.org/wiki/NAND_logic NAND] or [https://en.wikipedia.org/wiki/Sheffer_stroke Sheffer stroke] ) is the [[General Setwise Operations#Union|union]] of the complements. | ||

| Line 316: | Line 307: | ||

<span id="RelativeComplement"></span> | <span id="RelativeComplement"></span> | ||

==Relative Complement== | ==Relative Complement== | ||

| − | [[FILE:Venn0010.svg| | + | [[FILE:Venn0010.svg|border|right|thumb|240px|Relative Complement]] |

In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Complement_%28set_theory%29#Relative_complement relative complement] is denoted as: | In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Complement_%28set_theory%29#Relative_complement relative complement] is denoted as: | ||

| − | A<span style="vertical-align: super;">∁</span>&B = B\A | + | <span style="font-size: 140%;">A</span><span style="vertical-align: super;">∁</span><span style="font-size: 140%;"> ∩ B = B \ A</span> |

The relative complement is the [[General Setwise Operations#ComplementSet|absolute complement]] restricted to some other set. The relative complement of 'a' inside 'b' is also known as the '''set theoretic difference''' of 'b' minus 'a'. It is the set of all elements that belong to 'b' but '''not''' to 'a'. Also called 'b' without 'a'. It is the [[General Setwise Operations#Intersection|intersection]] of 'b' with the absolute complement of 'a'. | The relative complement is the [[General Setwise Operations#ComplementSet|absolute complement]] restricted to some other set. The relative complement of 'a' inside 'b' is also known as the '''set theoretic difference''' of 'b' minus 'a'. It is the set of all elements that belong to 'b' but '''not''' to 'a'. Also called 'b' without 'a'. It is the [[General Setwise Operations#Intersection|intersection]] of 'b' with the absolute complement of 'a'. | ||

not_a_in_b = ~a & b | not_a_in_b = ~a & b | ||

b_without_a = b & ~a | b_without_a = b & ~a | ||

| − | '''Truth Table''' | + | '''Truth Table'''<br/> |

Truth table of relative complement for one bit: | Truth table of relative complement for one bit: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 348: | Line 339: | ||

The relative complement of 'a' in 'b' may be interpreted as a bitwise (a < b) relation. | The relative complement of 'a' in 'b' may be interpreted as a bitwise (a < b) relation. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86]] don't has an own general purpose instruction for relative complement, but [[x86-64]] expansion [[BMI1]], and [[SIMD and SWAR Techniques|SIMD-instructions]]: | [[x86]] don't has an own general purpose instruction for relative complement, but [[x86-64]] expansion [[BMI1]], and [[SIMD and SWAR Techniques|SIMD-instructions]]: | ||

<pre> | <pre> | ||

| Line 357: | Line 348: | ||

vpandn ymm0, ymm1, ymm2 ; AVX xmm0 = ~xmm1 & xmm2 | vpandn ymm0, ymm1, ymm2 ; AVX xmm0 = ~xmm1 & xmm2 | ||

</pre> | </pre> | ||

| − | [[SSE2]]-intrinsic [ | + | [[SSE2]]-intrinsic [[SSE2#_mm_andnot_si128|_mm_andnot_si128]]<br/> |

| − | [[AVX2]]-intrinsic [ | + | [[AVX2]]-intrinsic [[AVX2#_mm256_andnot_si256|_mm256_andnot_si256]]<br/> |

[[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | ||

| − | '''Super minus Sub''' | + | '''Super minus Sub'''<br/> |

In presumption of [[General Setwise Operations#XorWithout|subtraction or exclusive or]] there are alternatives to calculate the relative complement - superset minus subset. We can take either the union without the complementing set - or the other set without the intersection | In presumption of [[General Setwise Operations#XorWithout|subtraction or exclusive or]] there are alternatives to calculate the relative complement - superset minus subset. We can take either the union without the complementing set - or the other set without the intersection | ||

~a & b == ( a | b ) - a | ~a & b == ( a | b ) - a | ||

| Line 367: | Line 358: | ||

==Implication== | ==Implication== | ||

| − | [[FILE:Venn1011.svg| | + | [[FILE:Venn1011.svg|border|right|thumb|240px|Implication]] |

Logical Implication or [https://en.wikipedia.org/wiki/Entailment Entailment] is denoted as: | Logical Implication or [https://en.wikipedia.org/wiki/Entailment Entailment] is denoted as: | ||

| − | A ⇒ B | + | <span style="font-size: 140%;">A ⇒ B</span> |

The boolean [https://en.wikipedia.org/wiki/Material_conditional Material conditional] is denoted as: | The boolean [https://en.wikipedia.org/wiki/Material_conditional Material conditional] is denoted as: | ||

| − | a → b | + | <span style="font-size: 140%;">a → b</span> |

Logical Implication or the boolean Material conditional 'a' implies 'b' (if 'a' then 'b') is an derived boolean operation, implemented as [[General Setwise Operations#Union|union]] of the [[General Setwise Operations#ComplementSet|absolute complement]] of 'a' with 'b': | Logical Implication or the boolean Material conditional 'a' implies 'b' (if 'a' then 'b') is an derived boolean operation, implemented as [[General Setwise Operations#Union|union]] of the [[General Setwise Operations#ComplementSet|absolute complement]] of 'a' with 'b': | ||

a_implies_b == ~a | b | a_implies_b == ~a | b | ||

| Line 400: | Line 391: | ||

Implication may be interpreted as a bitwise (a <= b) relation. | Implication may be interpreted as a bitwise (a <= b) relation. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

| − | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | + | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]]<br/> |

<span id="ExclusiveOr"></span> | <span id="ExclusiveOr"></span> | ||

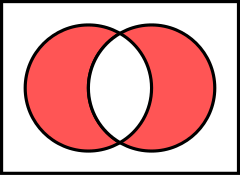

==Exclusive Or== | ==Exclusive Or== | ||

| − | [[FILE:Venn0110.svg| | + | [[FILE:Venn0110.svg|border|right|thumb|240px|Exclusive Or]] |

In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Symmetric_difference symmetric difference] is denoted as: | In [https://en.wikipedia.org/wiki/Set_theory set theory] [https://en.wikipedia.org/wiki/Symmetric_difference symmetric difference] is denoted as: | ||

| − | A ∆ B | + | <span style="font-size: 140%;">A ∆ B</span> |

In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Exclusive_or Exclusive or] is denoted as: | In [https://en.wikipedia.org/wiki/Boolean_algebra_%28logic%29 boolean algebra] [https://en.wikipedia.org/wiki/Exclusive_or Exclusive or] is denoted as: | ||

| − | a ⊕ b | + | <span style="font-size: 140%;">a ⊕ b</span> |

| − | Exclusive or, also exclusive disjunction (xor, binary operator '^' in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "XOR" in [[Pascal]]), also called symmetric difference, leaves all elements which are exclusively set in one of the two sets. Xor is really a multi purpose operation with a lot of applications not only bitboards of course. | + | Exclusive or, also exclusive disjunction (xor, binary operator '^' in [[C]], [[Cpp|C++]] or [[Java]], or the keyword "XOR" in [[Pascal]]), |

| + | xor = a ^ b | ||

| + | also called symmetric difference, leaves all elements which are exclusively set in one of the two sets. Xor is really a multi purpose operation with a lot of applications not only bitboards of course. | ||

<pre> | <pre> | ||

1 . . . . . . 1 . . . . . . . . 1 . . . . . . 1 | 1 . . . . . . 1 . . . . . . . . 1 . . . . . . 1 | ||

| Line 420: | Line 413: | ||

1 . . . . . . 1 . . . . . . . . 1 . . . . . . 1 | 1 . . . . . . 1 . . . . . . . . 1 . . . . . . 1 | ||

</pre> | </pre> | ||

| − | '''Truth Table''' | + | '''Truth Table''' <br/> |

Truth table of [https://en.wikipedia.org/wiki/XOR_gate exclusive or] for one bit: | Truth table of [https://en.wikipedia.org/wiki/XOR_gate exclusive or] for one bit: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 448: | Line 441: | ||

It also acts like a bitwise subtraction (modulo 2). | It also acts like a bitwise subtraction (modulo 2). | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise exclusive or: | [[x86]] has general purpose instruction as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for bitwise exclusive or: | ||

<pre> | <pre> | ||

| Line 457: | Line 450: | ||

vpxor ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 ^ ymm2 | vpxor ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 ^ ymm2 | ||

</pre> | </pre> | ||

| − | [[SSE2]]-intrinsic [ | + | [[SSE2]]-intrinsic [[SSE2#_mm_xor_si128|_mm_xor_si128]]<br/> |

| − | [[AVX2]]-intrinsic [ | + | [[AVX2]]-intrinsic [[AVX2#_mm256_xor_si256|_mm256_xor_si256]]<br/> |

[[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | ||

| − | '''Commutative''' | + | '''Commutative''' <br/> |

Exclusive disjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | Exclusive disjunction is [https://en.wikipedia.org/wiki/Commutative commutative] | ||

a ^ b == b ^ a | a ^ b == b ^ a | ||

| − | '''Associative''' | + | '''Associative'''<br/> |

Xor is [https://en.wikipedia.org/wiki/Associative associative] as well. | Xor is [https://en.wikipedia.org/wiki/Associative associative] as well. | ||

(a ^ b) ^ c == a ^ (b ^ c) | (a ^ b) ^ c == a ^ (b ^ c) | ||

| − | '''Distributive''' | + | |

| + | '''Distributive''' <br/> | ||

[[General Setwise Operations#Intersection|Conjunction]] is [https://en.wikipedia.org/wiki/Distributivity distributive] over exclusive disjunction - but '''not''' vice versa, since conjunction acts like multiplication, while xor acts as addition in the [https://en.wikipedia.org/wiki/Finite_field Galois field] [https://en.wikipedia.org/wiki/GF%282%29 GF(2)] : | [[General Setwise Operations#Intersection|Conjunction]] is [https://en.wikipedia.org/wiki/Distributivity distributive] over exclusive disjunction - but '''not''' vice versa, since conjunction acts like multiplication, while xor acts as addition in the [https://en.wikipedia.org/wiki/Finite_field Galois field] [https://en.wikipedia.org/wiki/GF%282%29 GF(2)] : | ||

x & (y ^ z) == (x & y) ^ (x & z) | x & (y ^ z) == (x & y) ^ (x & z) | ||

| − | '''Own Inverse''' | + | |

| + | '''Own Inverse''' <br/> | ||

If applied two (even) times with the same operand, xor restores the original result. It is own inverse or an [https://en.wikipedia.org/wiki/Involution involution] . | If applied two (even) times with the same operand, xor restores the original result. It is own inverse or an [https://en.wikipedia.org/wiki/Involution involution] . | ||

| − | '''Subset''' | + | |

| + | '''Subset'''<br/> | ||

If one operand is subset of the other, xor (or subtraction) implements the [[General Setwise Operations#RelativeComplement|relative complement]]. | If one operand is subset of the other, xor (or subtraction) implements the [[General Setwise Operations#RelativeComplement|relative complement]]. | ||

<pre> | <pre> | ||

| Line 485: | Line 481: | ||

. . . . . . . . . . . . . . . . . . . . . . . . | . . . . . . . . . . . . . . . . . . . . . . . . | ||

</pre> | </pre> | ||

| − | '''Subtraction''' | + | '''Subtraction'''<br/> |

While commutative, xor is a better replacement for subtracting from power of two minus one values, such as 63. | While commutative, xor is a better replacement for subtracting from power of two minus one values, such as 63. | ||

| − | (2 | + | (2<span style="vertical-align: super;">n</span> - 1) - a == a ^ (2<span style="vertical-align: super;">n</span> - 1) with a subset of 2<span style="vertical-align: super;">n</span> - 1 |

This is because it usually safes one [[x86]] load instruction and an additional register, but uses opcodes with immediate operands - for instance: | This is because it usually safes one [[x86]] load instruction and an additional register, but uses opcodes with immediate operands - for instance: | ||

<pre> | <pre> | ||

| Line 499: | Line 495: | ||

-1 - a == a ^ -1 | -1 - a == a ^ -1 | ||

</pre> | </pre> | ||

| − | '''Or without And''' | + | '''Or without And''' <br/> |

Xor is the same as a [[General Setwise Operations#Union|union]] without the [[General Setwise Operations#Intersection|intersection]] - all the bits different, 0,1 or 1,0. Since the [[General Setwise Operations#Intersection|intersection]] is subset of the [[General Setwise Operations#Union|union]], xor or subtraction can replace the "without" operation & ~: | Xor is the same as a [[General Setwise Operations#Union|union]] without the [[General Setwise Operations#Intersection|intersection]] - all the bits different, 0,1 or 1,0. Since the [[General Setwise Operations#Intersection|intersection]] is subset of the [[General Setwise Operations#Union|union]], xor or subtraction can replace the "without" operation & ~: | ||

a ^ b == (a | b) &~(a & b) | a ^ b == (a | b) &~(a & b) | ||

a ^ b == (a | b) ^ (a & b) | a ^ b == (a | b) ^ (a & b) | ||

a ^ b == (a | b) - (a & b) | a ^ b == (a | b) - (a & b) | ||

| − | '''Disjoint Sets''' | + | |

| + | '''Disjoint Sets''' <br/> | ||

The symmetric difference of disjoint sets is equal to the [[General Setwise Operations#Union|union]] or arithmetical addition. Since [[General Setwise Operations#Intersection|intersection]] and symmetric difference are disjoint, the union might defined that way: | The symmetric difference of disjoint sets is equal to the [[General Setwise Operations#Union|union]] or arithmetical addition. Since [[General Setwise Operations#Intersection|intersection]] and symmetric difference are disjoint, the union might defined that way: | ||

a | b = ( a & b ) ^ ( a ^ b ) | a | b = ( a & b ) ^ ( a ^ b ) | ||

| Line 511: | Line 508: | ||

a | b = ( a & b ) + ( a ^ b ) | a | b = ( a & b ) + ( a ^ b ) | ||

Assume we have distinct attack sets of pawns in left or right [[Direction|direction]]. The set of all squares attacked by two pawns is the intersection, the set exclusively attacked by one pawn (either right or left) is the xor-sum, while all squares attacked by any pawn is the union, see [[Pawn Attacks (Bitboards)#PawnAttacks|pawn attacks]]. | Assume we have distinct attack sets of pawns in left or right [[Direction|direction]]. The set of all squares attacked by two pawns is the intersection, the set exclusively attacked by one pawn (either right or left) is the xor-sum, while all squares attacked by any pawn is the union, see [[Pawn Attacks (Bitboards)#PawnAttacks|pawn attacks]]. | ||

| − | '''Union of Complements''' | + | |

| + | '''Union of Complements'''<br/> | ||

The symmetric difference is equivalent to the [[General Setwise Operations#Union|union]] of both [[General Setwise Operations#RelativeComplement|relative complements]]. Since both [[General Setwise Operations#RelativeComplement|relative complements]] are [https://en.wikipedia.org/wiki/Disjoint disjoint], bitwise or or add can replaced by xor itself: | The symmetric difference is equivalent to the [[General Setwise Operations#Union|union]] of both [[General Setwise Operations#RelativeComplement|relative complements]]. Since both [[General Setwise Operations#RelativeComplement|relative complements]] are [https://en.wikipedia.org/wiki/Disjoint disjoint], bitwise or or add can replaced by xor itself: | ||

a ^ b == (a & ~b) | (b & ~a) | a ^ b == (a & ~b) | (b & ~a) | ||

a ^ b == (a & ~b) ^ (b & ~a) | a ^ b == (a & ~b) ^ (b & ~a) | ||

a ^ b == (a & ~b) + (b & ~a) | a ^ b == (a & ~b) + (b & ~a) | ||

| − | '''Toggle''' | + | |

| + | '''Toggle''' <br/> | ||

Xor can be used to toggle or flip bits by a mask. | Xor can be used to toggle or flip bits by a mask. | ||

x ^= mask; | x ^= mask; | ||

| − | '''Complement''' | + | |

| + | '''Complement''' <br/> | ||

xor with the universal set -1 flips each bit and results in the ones' complement. | xor with the universal set -1 flips each bit and results in the ones' complement. | ||

a ^ -1 == ~a | a ^ -1 == ~a | ||

<span id="XorWithout"></span> | <span id="XorWithout"></span> | ||

| − | '''Without''' | + | '''Without''' <br/> |

Due to distributive law and since symmetric difference of set and subset is the relative complement of subset in set, there are some equivalent ways to calculate the [[General Setwise Operations#RelativeComplement|relative complement]] by xor. Based on surrounding expressions or whether subexpressions such as union, intersection or symmetric difference may be reused one may prefer the one or other alternative. | Due to distributive law and since symmetric difference of set and subset is the relative complement of subset in set, there are some equivalent ways to calculate the [[General Setwise Operations#RelativeComplement|relative complement]] by xor. Based on surrounding expressions or whether subexpressions such as union, intersection or symmetric difference may be reused one may prefer the one or other alternative. | ||

a & ~b == a & (-1 ^ b ) | a & ~b == a & (-1 ^ b ) | ||

| Line 529: | Line 529: | ||

a & ~b == a ^ ( a & b ) == a - ( a & b ) | a & ~b == a ^ ( a & b ) == a - ( a & b ) | ||

a & ~b == b ^ ( a | b ) == ( a | b ) - b | a & ~b == b ^ ( a | b ) == ( a | b ) - b | ||

| − | Also note that | + | Also note that<br/> |

a & a == a & -1 | a & a == a & -1 | ||

<span id="XorClear"></span> | <span id="XorClear"></span> | ||

| − | '''Clear''' | + | '''Clear'''<br/> |

Since 'a' xor 'a' is zero, it is the shorter opcode to clear a register, since it takes no immediate operand. Applied by optimizing compilers. Same is true for subtraction by the way. | Since 'a' xor 'a' is zero, it is the shorter opcode to clear a register, since it takes no immediate operand. Applied by optimizing compilers. Same is true for subtraction by the way. | ||

<pre> | <pre> | ||

| Line 539: | Line 539: | ||

pxor xmm0, xmm0 ; SSE2 - 128-bit xmm-register | pxor xmm0, xmm0 ; SSE2 - 128-bit xmm-register | ||

</pre> | </pre> | ||

| − | '''Xor Swap''' | + | '''Xor Swap'''<br/> |

Three xors on the same registers swap their content: (Note: this only works when a and b are stored on distinct memory adresses!) | Three xors on the same registers swap their content: (Note: this only works when a and b are stored on distinct memory adresses!) | ||

<pre> | <pre> | ||

| Line 554: | Line 554: | ||

... 'a' becomes 'b', but only a part of 'b', where mask is one, becomes 'a'. | ... 'a' becomes 'b', but only a part of 'b', where mask is one, becomes 'a'. | ||

<span id="BitsFrom2SourcesByMask"></span> | <span id="BitsFrom2SourcesByMask"></span> | ||

| − | '''Bits from two Sources''' | + | '''Bits from two Sources'''<br/> |

Getting arbitrary, [https://en.wikipedia.org/wiki/Disjoint disjoint] bits from two sources by a mask: | Getting arbitrary, [https://en.wikipedia.org/wiki/Disjoint disjoint] bits from two sources by a mask: | ||

<pre> | <pre> | ||

| Line 568: | Line 568: | ||

== (a & ~mask) + (b & mask) because both sets of the union are disjoint | == (a & ~mask) + (b & mask) because both sets of the union are disjoint | ||

</pre> | </pre> | ||

| − | '''XOR-applications and affairs''' | + | '''XOR-applications and affairs'''<br/> |

* Calculation of hash-keys based on [[Zobrist Hashing|Zobrist-keys]]. | * Calculation of hash-keys based on [[Zobrist Hashing|Zobrist-keys]]. | ||

* [https://en.wikipedia.org/wiki/Cyclic_redundancy_check Cyclic redundancy check], [[Parallel Prefix Algorithms#ParityWords|Parity words]] or [[Parallel Prefix Algorithms#GrayCode|Gray Code]] | * [https://en.wikipedia.org/wiki/Cyclic_redundancy_check Cyclic redundancy check], [[Parallel Prefix Algorithms#ParityWords|Parity words]] or [[Parallel Prefix Algorithms#GrayCode|Gray Code]] | ||

* [https://en.wikipedia.org/wiki/Fredkin_gate Fredkin gate] by [[Edward Fredkin]] | * [https://en.wikipedia.org/wiki/Fredkin_gate Fredkin gate] by [[Edward Fredkin]] | ||

* [[Hyperbola Quintessence]]. | * [[Hyperbola Quintessence]]. | ||

| − | * [[Subtracting a | + | * [[Subtracting a Rook from a Blocking Piece|o^(o-2r)]]. |

* [[Robert Hyatt|Robert Hyatt's]] approach of a [[Shared Hash Table#Lockless|lockless transposition table]] | * [[Robert Hyatt|Robert Hyatt's]] approach of a [[Shared Hash Table#Lockless|lockless transposition table]] | ||

* [[General Setwise Operations#SwappingBits|Swapping Bits]]. | * [[General Setwise Operations#SwappingBits|Swapping Bits]]. | ||

| Line 579: | Line 579: | ||

==Equivalence== | ==Equivalence== | ||

| − | [[FILE:Venn1001.svg| | + | [[FILE:Venn1001.svg|border|right|thumb|240px|Equivalence]] |

| − | + | [https://en.wikipedia.org/wiki/If_and_only_if If and only if] (Iff) is denoted as: | |

| − | [https://en.wikipedia.org/wiki/If_and_only_if If and only if] is denoted as: | + | <span style="font-size: 140%;">A ⇔ B</span> |

| − | A ⇔ B | ||

[https://en.wikipedia.org/wiki/Logical_equivalence Logical equivalence] is denoted as: | [https://en.wikipedia.org/wiki/Logical_equivalence Logical equivalence] is denoted as: | ||

| − | a ↔ b | + | <span style="font-size: 140%;">a ↔ b</span> |

[https://en.wikipedia.org/wiki/Logical_equality Logical equality], [https://en.wikipedia.org/wiki/Logical_equivalence logical equivalence] or [https://en.wikipedia.org/wiki/Logical_biconditional biconditional] ([https://en.wikipedia.org/wiki/If_and_only_if if and only if], [https://en.wikipedia.org/wiki/XNOR_gate XNOR] ) is the complement of xor. | [https://en.wikipedia.org/wiki/Logical_equality Logical equality], [https://en.wikipedia.org/wiki/Logical_equivalence logical equivalence] or [https://en.wikipedia.org/wiki/Logical_biconditional biconditional] ([https://en.wikipedia.org/wiki/If_and_only_if if and only if], [https://en.wikipedia.org/wiki/XNOR_gate XNOR] ) is the complement of xor. | ||

| Line 590: | Line 589: | ||

a_equal_b == (a & b) | (~a & ~b) | a_equal_b == (a & b) | (~a & ~b) | ||

a_equal_b == (a & b) | ~(a | b) | a_equal_b == (a & b) | ~(a | b) | ||

| − | '''Truth Table''' | + | '''Truth Table''' <br/> |

Truth table of equivalence or for one bit: | Truth table of equivalence or for one bit: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 616: | Line 615: | ||

Equivalence implements a bitwise (a == b) relation. | Equivalence implements a bitwise (a == b) relation. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

| − | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]] | + | [[AVX-512]] has [[AVX-512#VPTERNLOG|VPTERNLOG]]<br/> |

<span id="Majority"></span> | <span id="Majority"></span> | ||

==Majority== | ==Majority== | ||

The [https://en.wikipedia.org/wiki/Majority_function majority function] or '''median operator''' is a function from n inputs to one output. The value of the operation is false when n/2 or fewer arguments are false, and true otherwise. For two inputs it is the [[General Setwise Operations#Intersection|intersection]]. Three inputs require some more computation: | The [https://en.wikipedia.org/wiki/Majority_function majority function] or '''median operator''' is a function from n inputs to one output. The value of the operation is false when n/2 or fewer arguments are false, and true otherwise. For two inputs it is the [[General Setwise Operations#Intersection|intersection]]. Three inputs require some more computation: | ||

| − | '''Truth Table''' | + | '''Truth Table'''<br/> |

Truth table of majority for three inputs: | Truth table of majority for three inputs: | ||

{| class="wikitable" | {| class="wikitable" | ||

| Line 674: | Line 673: | ||

See the application of [[Population Count#CardinalityofMultipleSets|cardinality of multiple sets]] for more than three inputs. | See the application of [[Population Count#CardinalityofMultipleSets|cardinality of multiple sets]] for more than three inputs. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[AVX-512]] [[AVX-512#VPTERNLOG|VPTERNLOG]] imm8 = 0xe8 implements the majority function. | [[AVX-512]] [[AVX-512#VPTERNLOG|VPTERNLOG]] imm8 = 0xe8 implements the majority function. | ||

<span id="GreaterOne"></span> | <span id="GreaterOne"></span> | ||

==Greater One Sets== | ==Greater One Sets== | ||

'''Greater One''' is a function from n inputs to one output. The value of the operation is true if more than one argument is true, false otherwise. Obviously, for two inputs it is the [[General Setwise Operations#Intersection|intersection]], for three inputs it is the [[General Setwise Operations#Majority|majority function]]. For more inputs it is the union of all distinct pairwise intersections, which can be expressed with setwise operators that way: | '''Greater One''' is a function from n inputs to one output. The value of the operation is true if more than one argument is true, false otherwise. Obviously, for two inputs it is the [[General Setwise Operations#Intersection|intersection]], for three inputs it is the [[General Setwise Operations#Majority|majority function]]. For more inputs it is the union of all distinct pairwise intersections, which can be expressed with setwise operators that way: | ||

| − | <span style="font-size: 200%;">∪</span><span style="vertical-align: sub;">i>j∈I</span><span style="font-size: 120%;">(A<span style="vertical-align: sub;">i</span>∩A<span style="vertical-align: sub;">j</span>)</span> | + | <span style="font-size: 200%;">∪</span><span style="vertical-align: sub;">i>j∈I</span><span style="font-size: 120%;">(A<span style="vertical-align: sub;">i</span> ∩ A<span style="vertical-align: sub;">j</span>)</span> |

With four bitboards this is equivalent to: | With four bitboards this is equivalent to: | ||

<pre> | <pre> | ||

| Line 696: | Line 695: | ||

operations - that is 11 for n == 4. | operations - that is 11 for n == 4. | ||

| − | '''O(n^2) to O(n)''' | + | '''O(n^2) to O(n)''' <br/> |

Due to [[General Setwise Operations#DistributiveAndOr|distibutive law]] one can factor out common sets ... | Due to [[General Setwise Operations#DistributiveAndOr|distibutive law]] one can factor out common sets ... | ||

<pre> | <pre> | ||

| Line 705: | Line 704: | ||

... with further reductions of the number of operations, also due to aggregation of the inner or-terms. Three additional operations for an increment of n, thus the former quadratic increase becomes linear. | ... with further reductions of the number of operations, also due to aggregation of the inner or-terms. Three additional operations for an increment of n, thus the former quadratic increase becomes linear. | ||

| − | In general, as mentioned, | + | In general, as mentioned,<br/> |

| − | <span style="font-size: 200%;">∪</span><span style="vertical-align: sub;">i>j∈I</span><span style="font-size: 120%;">(A<span style="vertical-align: sub;">i</span>∩A<span style="vertical-align: sub;">j</span>)</span> | + | <span style="font-size: 200%;">∪</span><span style="vertical-align: sub;">i>j∈I</span><span style="font-size: 120%;">(A<span style="vertical-align: sub;">i</span> ∩ A<span style="vertical-align: sub;">j</span>)</span> |

requires | requires | ||

n * (n - 1) - 1 | n * (n - 1) - 1 | ||

| Line 750: | Line 749: | ||

The reason the bitboard type-definintion is unsigned in [[C]], [[Cpp|C++]] is to avoid so called [https://en.wikipedia.org/wiki/Arithmetic_shift arithmetical shift right] in opposition to [https://en.wikipedia.org/wiki/Logical_shift logical shift right] . Arithmetical shift right implies filling one-bits in from MSB-direction if the operand is negative and has MSB bit 63 set. Logical shift right always shifts in zeros - that is what we need. [[Java]] has no unsigned types, but a special unsigned shift right operator >>>. | The reason the bitboard type-definintion is unsigned in [[C]], [[Cpp|C++]] is to avoid so called [https://en.wikipedia.org/wiki/Arithmetic_shift arithmetical shift right] in opposition to [https://en.wikipedia.org/wiki/Logical_shift logical shift right] . Arithmetical shift right implies filling one-bits in from MSB-direction if the operand is negative and has MSB bit 63 set. Logical shift right always shifts in zeros - that is what we need. [[Java]] has no unsigned types, but a special unsigned shift right operator >>>. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

| − | [[x86]] has general purpose | + | [[x86]] has general purpose instructions, [[BMI2]] general purpose instructions not affecting processor flags, as well as [[SIMD and SWAR Techniques|SIMD-instructions]] for various shifts: |

<pre> | <pre> | ||

shr rax, cl ; rax >>= cl | shr rax, cl ; rax >>= cl | ||

shl rax, cl ; rax <<= cl | shl rax, cl ; rax <<= cl | ||

| + | shrx r64a, r/m64, r64b; BMI2 r64a = r/m64 >> r64b | ||

| + | shlx r64a, r/m64, r64b; BMI2 r64a = r/m64 << r64b | ||

psrlq mm0, mm1 ; MMX mm0 >>= mm1 | psrlq mm0, mm1 ; MMX mm0 >>= mm1 | ||

psllq mm0, mm1 ; MMX mm0 <<= mm1 | psllq mm0, mm1 ; MMX mm0 <<= mm1 | ||

psrlq xmm0, xmm1 ; SSE2 xmm0 >>= xmm1 | psrlq xmm0, xmm1 ; SSE2 xmm0 >>= xmm1 | ||

psllq xmm0, xmm1 ; SSE2 xmm0 <<= xmm1 | psllq xmm0, xmm1 ; SSE2 xmm0 <<= xmm1 | ||

| − | |||

| − | |||

vpsrlvq ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 >> ymm2 ; Individual shifts | vpsrlvq ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 >> ymm2 ; Individual shifts | ||

vpsllvq ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 << ymm2 ; Individual shifts | vpsllvq ymm0, ymm1, ymm2 ; AVX2 ymm0 = ymm1 << ymm2 ; Individual shifts | ||

</pre> | </pre> | ||

[[SSE2]]-intrinsics with variable register or constant immediate shift amounts, working on vectors of two bitboards: | [[SSE2]]-intrinsics with variable register or constant immediate shift amounts, working on vectors of two bitboards: | ||

| − | * [ | + | * [[SSE2#_mm_srl_epi64|_mm_srl_epi64]] |

| − | * [ | + | * [[SSE2#_mm_srli_epi64|_mm_srli_epi64]] |

| − | + | * [[SSE2#_mm_sll_epi64|_mm_sll_epi64]] | |

| − | * | + | * [[SSE2#_mm_slli_epi64|_mm_slli_epi64]] |

| − | |||

| − | |||

| − | * [ | ||

| − | |||

[[AVX2]] has [[AVX2#IndividualShifts|individual shifts]] for each of four bitboards: | [[AVX2]] has [[AVX2#IndividualShifts|individual shifts]] for each of four bitboards: | ||

| − | * [ | + | * [[AVX2#_mm256_sllv_epi64|_mm256_sllv_epi64]] |

| − | * [ | + | * [[AVX2#_mm256_srlv_epi64|_mm256_srlv_epi64]] |

<span id="OneStepOnly"></span> | <span id="OneStepOnly"></span> | ||

==One Step Only== | ==One Step Only== | ||

| Line 831: | Line 826: | ||

</pre> | </pre> | ||

| − | Most processors have rotate instructions, but are not supported by standard programming languages like [[C]] or [[Java]]. Some compilers provide | + | Most processors have rotate instructions, but are not supported by standard programming languages like [[C]] or [[Java]]. Some compilers provide intrinsic, processor specific functions. |

<pre> | <pre> | ||

U64 rotateLeft (U64 x, int s) {return _rotl64(x, s);} | U64 rotateLeft (U64 x, int s) {return _rotl64(x, s);} | ||

| Line 841: | Line 836: | ||

ror rax, cl | ror rax, cl | ||

</pre> | </pre> | ||

| − | '''Rotate by Shift''' | + | '''Rotate by Shift'''<br/> |

Otherwise rotate has to be emulated by shifts, with some chance optimizing compiler will emit exactly one rotate instruction. | Otherwise rotate has to be emulated by shifts, with some chance optimizing compiler will emit exactly one rotate instruction. | ||

<pre> | <pre> | ||

| Line 889: | Line 884: | ||

</pre> | </pre> | ||

<span id="GenOneStep"></span> | <span id="GenOneStep"></span> | ||

| − | '''One Step''' | + | '''One Step'''<br/> |

[[x86-64]] rot64 works like a generalized shift with positive or negative shift amount - since it internally applies an unsigned modulo 64 ( & 63) and makes -i = 64-i. We need to clear either the lower or upper bits by intersection with a mask, which might be combined with the wrap-ands for [[General Setwise Operations#OneStepOnly|one step]]. It might be applied to get attacks for both sides with a [[Direction|direction]] parameter and small lookups for shift amount and wrap-ands - instead of multiple code for eight directions. Of course generalized shift will be a bit slower due to lookups and using cl as the shift amount register. | [[x86-64]] rot64 works like a generalized shift with positive or negative shift amount - since it internally applies an unsigned modulo 64 ( & 63) and makes -i = 64-i. We need to clear either the lower or upper bits by intersection with a mask, which might be combined with the wrap-ands for [[General Setwise Operations#OneStepOnly|one step]]. It might be applied to get attacks for both sides with a [[Direction|direction]] parameter and small lookups for shift amount and wrap-ands - instead of multiple code for eight directions. Of course generalized shift will be a bit slower due to lookups and using cl as the shift amount register. | ||

<pre> | <pre> | ||

| Line 957: | Line 952: | ||

''The inverse function square = log2(x), is topic of [[BitScan|bitscan]] and [[Bitboard Serialization|bitboard serialization]].'' | ''The inverse function square = log2(x), is topic of [[BitScan|bitscan]] and [[Bitboard Serialization|bitboard serialization]].'' | ||

| − | '''Shift versus Lookup''' | + | '''Shift versus Lookup''' <br/> |

While 1 << square sounds cheap, it is rather expensive in 32-bit mode - and therefor often precalculated in a small lookup-table of 64-single bit bitboards. Also, on [[x86-64]]-processors a variable shift is restricted to the byte-register cl. Thus, two or more variable shifts are constrained by sequential execution <ref>[http://www.open-chess.org/viewtopic.php?f=5&t=2878 To shift or not to shift] by thevinenator, [[Computer Chess Forums|OpenChess Forum]], September 09, 2015</ref>. | While 1 << square sounds cheap, it is rather expensive in 32-bit mode - and therefor often precalculated in a small lookup-table of 64-single bit bitboards. Also, on [[x86-64]]-processors a variable shift is restricted to the byte-register cl. Thus, two or more variable shifts are constrained by sequential execution <ref>[http://www.open-chess.org/viewtopic.php?f=5&t=2878 To shift or not to shift] by thevinenator, [[Computer Chess Forums|OpenChess Forum]], September 09, 2015</ref>. | ||

| − | '''Test''' | + | '''Test''' <br/> |

Test a bit of a square-index by [[General Setwise Operations#Intersection|intersection]]-operator 'and'. | Test a bit of a square-index by [[General Setwise Operations#Intersection|intersection]]-operator 'and'. | ||

<pre> | <pre> | ||

if (x & singleBitset) -> bit is set; | if (x & singleBitset) -> bit is set; | ||

</pre> | </pre> | ||

| − | '''Set''' | + | '''Set''' <br/> |

Set a bit of a square-index by [[General Setwise Operations#Union|union]]-operator 'or'. | Set a bit of a square-index by [[General Setwise Operations#Union|union]]-operator 'or'. | ||

<pre> | <pre> | ||

x |= singleBitset; // set bit | x |= singleBitset; // set bit | ||

</pre> | </pre> | ||

| − | '''Toggle''' | + | '''Toggle''' <br/> |

Toggle a bit of square-index by [[General Setwise Operations#ExclusiveOr|xor]]. | Toggle a bit of square-index by [[General Setwise Operations#ExclusiveOr|xor]]. | ||

<pre> | <pre> | ||

x ^= singleBitset; // toggle bit | x ^= singleBitset; // toggle bit | ||

</pre> | </pre> | ||

| − | '''Reset''' | + | '''Reset''' <br/> |

| − | Reset a bit of square-index by [[General Setwise Operations#RelativeComplement|relative complement]] of the single bit | + | <span id="ResetBit"></span>Reset a bit of square-index by [[General Setwise Operations#RelativeComplement|relative complement]] of the single bit, |

<pre> | <pre> | ||

x &= ~singleBitset; // reset bit | x &= ~singleBitset; // reset bit | ||

| + | </pre> | ||

| + | or conditional toggle by single bit intersection | ||

| + | <pre> | ||

| + | x ^= singleBitset & x; // reset bit | ||

</pre> | </pre> | ||

Set and toggle (or, xor) might the faster way to reset a bit inside a register (not, and). | Set and toggle (or, xor) might the faster way to reset a bit inside a register (not, and). | ||

| Line 987: | Line 986: | ||

If singleBitset needs to preserved, an extra register is needed for the complement. | If singleBitset needs to preserved, an extra register is needed for the complement. | ||

| − | '''x86-Instructions''' | + | '''x86-Instructions''' <br/> |

| − | [[x86]] processor provides a bit-test instruction family (bt, bts, btr, btc) with 32- and 64-bit operands. They may be used implicitly by compiler optimization or explicitly by inline assembler or compiler intrinsics. Take care that they are applied on local variables likely registers rather than memory references | + | [[x86]] processor provides a bit-test instruction family (bt, bts, btr, btc) with 32- and 64-bit operands. They may be used implicitly by compiler optimization or explicitly by inline assembler or compiler intrinsics. Take care that they are applied on local variables likely registers rather than memory references <ref>[https://groups.google.com/forum/#!topic/fishcooking/TplkvO62I9U On the speed of SquareBB array] by protonspring, [[Computer Chess Forums|FishCooking]], March 22, 2019</ref>: |

| − | + | * [[x86-64#gpinstructions|_bittest64]] | |

| − | * [ | + | * [[x86-64#gpinstructions|_bittestandset64]] |

| − | * [ | + | * [[x86-64#gpinstructions|_bittestandcomplement64]] |

| − | * [ | + | * [[x86-64#gpinstructions|_bittestandreset64]] |

<span id="UpdateByMove"></span> | <span id="UpdateByMove"></span> | ||

==Update by Move== | ==Update by Move== | ||

| Line 1,023: | Line 1,022: | ||

Similar for special moves like [[Castling|castling]], [[Promotions|promotions]] and [[En passant|en passant captures]]. | Similar for special moves like [[Castling|castling]], [[Promotions|promotions]] and [[En passant|en passant captures]]. | ||

<span id="UpperAndLowerBits"></span> | <span id="UpperAndLowerBits"></span> | ||

| − | '''Upper Squares''' | + | '''Upper Squares''' <br/> |

To get a set of all upper squares or bits, either shift ~1 or -2 left by square: | To get a set of all upper squares or bits, either shift ~1 or -2 left by square: | ||

<pre> | <pre> | ||

| Line 1,041: | Line 1,040: | ||

</pre> | </pre> | ||

| − | '''Lower Squares''' | + | '''Lower Squares''' <br/> |

Lower squares are simply Bit by Square minus one. | Lower squares are simply Bit by Square minus one. | ||

<pre> | <pre> | ||

| Line 1,062: | Line 1,061: | ||

[http://graphics.stanford.edu/%7Eseander/bithacks.html#SwappingBitsXOR Swapping] none overlapping bit-sequences in a bitboard is the base of a lot of [https://en.wikipedia.org/wiki/Permutation permutation] tricks. | [http://graphics.stanford.edu/%7Eseander/bithacks.html#SwappingBitsXOR Swapping] none overlapping bit-sequences in a bitboard is the base of a lot of [https://en.wikipedia.org/wiki/Permutation permutation] tricks. | ||

| − | '''by Position''' | + | '''by Position'''<br/> |

Suppose we like to swap n [[Bit|bits]] from two none overlapping bit locations of a bitboard. The trick is to set all n least significant bits by subtracting one from n power of 2. Both substrings are shifted to bit zero, exclusive ored and masked by the n ones. This sequence is then twice shifted back to their original places, while the [[General Setwise Operations#Union|union]] (xor-union due to [https://en.wikipedia.org/wiki/Disjoint disjoint] bits) is finally exclusive ored with the original bitboard to swap both sequences. | Suppose we like to swap n [[Bit|bits]] from two none overlapping bit locations of a bitboard. The trick is to set all n least significant bits by subtracting one from n power of 2. Both substrings are shifted to bit zero, exclusive ored and masked by the n ones. This sequence is then twice shifted back to their original places, while the [[General Setwise Operations#Union|union]] (xor-union due to [https://en.wikipedia.org/wiki/Disjoint disjoint] bits) is finally exclusive ored with the original bitboard to swap both sequences. | ||

<pre> | <pre> | ||

| Line 1,111: | Line 1,110: | ||

</pre> | </pre> | ||

<span id="DeltaSwap"></span> | <span id="DeltaSwap"></span> | ||

| − | '''Delta Swap''' | + | '''Delta Swap''' <br/> |

To swap any none overlapping pairs we can shift by the difference (j-i, with j>i) and supply an explicit mask with a '1' on the least significant position for each pair supposed to be swapped. | To swap any none overlapping pairs we can shift by the difference (j-i, with j>i) and supply an explicit mask with a '1' on the least significant position for each pair supposed to be swapped. | ||

<pre> | <pre> | ||

| Line 1,143: | Line 1,142: | ||

<span id="ArithmeticalOperations"></span> | <span id="ArithmeticalOperations"></span> | ||

=Arithmetic Operations= | =Arithmetic Operations= | ||

| − | At the first glance, [https://en.wikipedia.org/wiki/Arithmetic#Arithmetic_operations arithmetic operations], that is [https://en.wikipedia.org/wiki/Addition addition], [https://en.wikipedia.org/wiki/Subtraction subtraction], [https://en.wikipedia.org/wiki/Multiplication multiplication] and [https://en.wikipedia.org/wiki/Division_%28mathematics%29 division], doesn't make much sense with bitboards. Still, there are some [[Bit-Twiddling|bit-twiddling]] applications related to least significant one bit (LS1B), to [[Traversing Subsets of a Set|enumerate all subsets of a set]] or [[Subtracting a | + | At the first glance, [https://en.wikipedia.org/wiki/Arithmetic#Arithmetic_operations arithmetic operations], that is [https://en.wikipedia.org/wiki/Addition addition], [https://en.wikipedia.org/wiki/Subtraction subtraction], [https://en.wikipedia.org/wiki/Multiplication multiplication] and [https://en.wikipedia.org/wiki/Division_%28mathematics%29 division], doesn't make much sense with bitboards. Still, there are some [[Bit-Twiddling|bit-twiddling]] applications related to least significant one bit (LS1B), to [[Traversing Subsets of a Set|enumerate all subsets of a set]] or [[Subtracting a Rook from a Blocking Piece|sliding attack generation]]. Multiplication of certain pattern has some applications as well, most likely to calculate hash-indicies of [[Occupancy of any Line#Multiplication|masked occupancies]]. |

==Derived from Bitwise== | ==Derived from Bitwise== | ||

| + | [[FILE:Half Adder.svg|border|right|thumb|link=https://en.wikipedia.org/wiki/Half_adder#Half_adder|Half Adder]] | ||

Unlike bitwise boolean operations on 64-bit words, which are in fact 64 parallel operations on each bit without any interaction between them, arithmetic operations like addition need to propagate possible [https://en.wikipedia.org/wiki/Carry_%28arithmetic%29 carries] from lower to higher bits. Despite, Add and Sub are usually as fast their bitwise boolean counterparts, because they are implemented in Hardware within the [[Combinatorial Logic#ALU|ALU]] of the CPU. A so called [[Combinatorial Logic#Adder|half-adder]] to add two bits (A, B), requires an [[Combinatorial Logic#AND|And-Gate]] for the carry (C) and a [[Combinatorial Logic#XOR|Xor-Gate]] for the sum (S): | Unlike bitwise boolean operations on 64-bit words, which are in fact 64 parallel operations on each bit without any interaction between them, arithmetic operations like addition need to propagate possible [https://en.wikipedia.org/wiki/Carry_%28arithmetic%29 carries] from lower to higher bits. Despite, Add and Sub are usually as fast their bitwise boolean counterparts, because they are implemented in Hardware within the [[Combinatorial Logic#ALU|ALU]] of the CPU. A so called [[Combinatorial Logic#Adder|half-adder]] to add two bits (A, B), requires an [[Combinatorial Logic#AND|And-Gate]] for the carry (C) and a [[Combinatorial Logic#XOR|Xor-Gate]] for the sum (S): | ||

| − | |||

| − | |||

<pre> | <pre> | ||

two_bitsum = (bitA ^ bitB) | ((bitA & bitB) << 1); | two_bitsum = (bitA ^ bitB) | ((bitA & bitB) << 1); | ||

| Line 1,192: | Line 1,190: | ||

<span id="Subtraction"></span> | <span id="Subtraction"></span> | ||

==Subtraction== | ==Subtraction== | ||

| − | [https://en.wikipedia.org/wiki/Subtraction Subtraction] (like xor) might be used to implement the [[General Setwise Operations#RelativeComplement|relative complement]], of a [https://en.wikipedia.org/wiki/Subset subset] inside it's superset. As mentioned, subtraction may be useful in calculating [[Subtracting a | + | [https://en.wikipedia.org/wiki/Subtraction Subtraction] (like xor) might be used to implement the [[General Setwise Operations#RelativeComplement|relative complement]], of a [https://en.wikipedia.org/wiki/Subset subset] inside it's superset. As mentioned, subtraction may be useful in calculating [[Subtracting a Rook from a Blocking Piece|sliding attacks]]. |

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

<pre> | <pre> | ||

sub rax, rbx ; rax -= rbx | sub rax, rbx ; rax -= rbx | ||

| Line 1,202: | Line 1,200: | ||

A lot of [[Bit-Twiddling|bit-twiddling]] tricks on bitboards to traverse or isolate subsets, rely on [https://en.wikipedia.org/wiki/Two%27s_complement two's complement] arithmetic. Most recent processors (and compiler or interpreter for these processors) use the two's complement to implement the unary minus operator for signed as well for unsigned integer types. In [[C]] it is guaranteed for unsigned integer types. [[Java]] guarantees two's complement for all implicit signed integral types char, short, int, long. | A lot of [[Bit-Twiddling|bit-twiddling]] tricks on bitboards to traverse or isolate subsets, rely on [https://en.wikipedia.org/wiki/Two%27s_complement two's complement] arithmetic. Most recent processors (and compiler or interpreter for these processors) use the two's complement to implement the unary minus operator for signed as well for unsigned integer types. In [[C]] it is guaranteed for unsigned integer types. [[Java]] guarantees two's complement for all implicit signed integral types char, short, int, long. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

<pre> | <pre> | ||

neg rax; rax = -rax; rax *= -1 | neg rax; rax = -rax; rax *= -1 | ||

</pre> | </pre> | ||

| − | ''2^N is used as power operator in this paragraph not xor | + | ''2^N is used as power operator in this paragraph not xor'' ! |

| − | '''Increment of Complement''' | + | '''Increment of Complement'''<br/> |

| − | The two's complement is defined as a value, we need to add to the original value to get 2 | + | The two's complement is defined as a value, we need to add to the original value to get 2<span style="vertical-align: super;">64</span> which is an "overflowed" zero - since all 64-bit values are implicitly modulo 2<span style="vertical-align: super;">64</span>. Thus, the two's complement is defined as ''ones' complement plus one'': |

| − | + | -x == ~x + 1 | |

| − | -x == ~x + 1 | + | That fulfills the condition that x + (-x) == 2<span style="vertical-align: super;">bitsize</span> (2<span style="vertical-align: super;">64</span>) which overflows to zero: |

| − | |||

| − | That fulfills the condition that x + (-x) == 2 | ||

<pre> | <pre> | ||

x + (-x) == 0 | x + (-x) == 0 | ||

| Line 1,220: | Line 1,216: | ||

==> x + ~x == -1 the universal set | ==> x + ~x == -1 the universal set | ||

</pre> | </pre> | ||

| − | '''Complement of Decrement''' | + | '''Complement of Decrement'''<br/> |

Replacing x by x - 1 in the increment of complement formula, leaves another definition - two's complement or Negation is also the ones' complement of the ones' decrement: | Replacing x by x - 1 in the increment of complement formula, leaves another definition - two's complement or Negation is also the ones' complement of the ones' decrement: | ||

| − | + | -x == ~(x - 1) | |

| − | -x == ~(x - 1) | ||

| − | |||

Thus, we can reduce subtraction by addition and ones' complement: | Thus, we can reduce subtraction by addition and ones' complement: | ||

<pre> | <pre> | ||

| Line 1,230: | Line 1,224: | ||

x - y == ~(~x + y) | x - y == ~(~x + y) | ||

</pre> | </pre> | ||

| − | + | '''Bitwise Copy/Invert'''<br/> | |

| − | '''Bitwise Copy/Invert''' | ||

The two's complement may also defined by a bitwise copy-loop from right (LSB) to left (MSB): | The two's complement may also defined by a bitwise copy-loop from right (LSB) to left (MSB): | ||

<pre> | <pre> | ||

| Line 1,239: | Line 1,232: | ||

</pre> | </pre> | ||

| − | '''Signed-Unsigned''' | + | '''Signed-Unsigned''' <br/> |

This works independently whether we interpret 'x' as signed or unsigned. While 0 is is the synonym for all bits clear, -1 is the synonym for all bits set in a computer word of any arbitrary bit-size, also for 64-bit words such as bitboards. | This works independently whether we interpret 'x' as signed or unsigned. While 0 is is the synonym for all bits clear, -1 is the synonym for all bits set in a computer word of any arbitrary bit-size, also for 64-bit words such as bitboards. | ||

| Line 1,302: | Line 1,295: | ||

Some C++ compiler warn -x still unsigned - (0-x) may used to avoid that with no overhead. | Some C++ compiler warn -x still unsigned - (0-x) may used to avoid that with no overhead. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[x86-64]] expansion [[BMI1]] has LS1B bit isolation: | [[x86-64]] expansion [[BMI1]] has LS1B bit isolation: | ||

<pre> | <pre> | ||

blsi rax, rbx ; BMI1 rax = rbx & -rbx | blsi rax, rbx ; BMI1 rax = rbx & -rbx | ||

</pre> | </pre> | ||

| − | [[BMI1]]-intrinsic [ | + | [[BMI1]]-intrinsic [[BMI1#_blsi_u3264|_blsi_u32/64]] |

[[AMD|AMD's]] [[x86-64]] expansion [[TBM]] further has a [[TBM#BLSIC|Isolate Lowest Set Bit and Complement]] instruction, which applies [[General Setwise Operations#DeMorganslaws|De Morgan's law]] to get the complement of the LS1B: | [[AMD|AMD's]] [[x86-64]] expansion [[TBM]] further has a [[TBM#BLSIC|Isolate Lowest Set Bit and Complement]] instruction, which applies [[General Setwise Operations#DeMorganslaws|De Morgan's law]] to get the complement of the LS1B: | ||

| Line 1,333: | Line 1,326: | ||

... since we already know two's complement (-x) and ones' decrement (x-1) are complement sets. | ... since we already know two's complement (-x) and ones' decrement (x-1) are complement sets. | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics'''<br/> |

[[x86-64]] expansion [[BMI1]] has LS1B bit reset: | [[x86-64]] expansion [[BMI1]] has LS1B bit reset: | ||

<pre> | <pre> | ||

blsr rax, rbx ; BMI1 rax = rbx & (rbx - 1) | blsr rax, rbx ; BMI1 rax = rbx & (rbx - 1) | ||

</pre> | </pre> | ||

| − | [[BMI1]]-intrinsic [ | + | [[BMI1]]-intrinsic [[BMI1#_blsr_u3264|_blsr_u32/64]] |

<span id="LS1BSeparation"></span> | <span id="LS1BSeparation"></span> | ||

===Separation=== | ===Separation=== | ||

| Line 1,379: | Line 1,372: | ||

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ||

</pre> | </pre> | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics'''<br/> |

[[x86-64]] expansion [[BMI1]] has [[BMI1#BLSMSK|BLSMSK]] (Mask Up to Lowest Set Bit = below_LSB1_mask_including), [[AMD|AMD's]] [[x86-64]] expansion [[TBM]] has [[TBM#TZMSK|TZMSK]] (Mask From Trailing Zeros = below_LSB1_mask): | [[x86-64]] expansion [[BMI1]] has [[BMI1#BLSMSK|BLSMSK]] (Mask Up to Lowest Set Bit = below_LSB1_mask_including), [[AMD|AMD's]] [[x86-64]] expansion [[TBM]] has [[TBM#TZMSK|TZMSK]] (Mask From Trailing Zeros = below_LSB1_mask): | ||

<pre> | <pre> | ||

| Line 1,385: | Line 1,378: | ||

tzmsk rax, rbx ; TBM: rax = ~rbx & (rbx - 1) | tzmsk rax, rbx ; TBM: rax = ~rbx & (rbx - 1) | ||

</pre> | </pre> | ||

| − | [[BMI1]]-intrinsic [ | + | [[BMI1]]-intrinsic [[BMI1#_blsmsk_u3264|_blsmsk_u32/64]] |

===Smearing=== | ===Smearing=== | ||

| Line 1,415: | Line 1,408: | ||

. . . . . . . . 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | . . . . . . . . 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ||

</pre> | </pre> | ||

| − | '''x86-mnemonics''' | + | '''x86-mnemonics''' <br/> |

[[AMD|AMD's]] [[x86-64]] expansion [[TBM]] has a [[TBM#BLSFILL|Fill From Lowest Set Bit]] instruction: | [[AMD|AMD's]] [[x86-64]] expansion [[TBM]] has a [[TBM#BLSFILL|Fill From Lowest Set Bit]] instruction: | ||

<pre> | <pre> | ||

| Line 1,445: | Line 1,438: | ||

Still quite expensive - better to traverse sets the other way around or rely on intrinsic functions to use special processor instructions like [[BitScan#Bitscanreverse|BitScanReverse]] or LeadingZeroCount, which implicitly performs not only the isolation but also the [https://en.wikipedia.org/wiki/Binary_logarithm log2]. | Still quite expensive - better to traverse sets the other way around or rely on intrinsic functions to use special processor instructions like [[BitScan#Bitscanreverse|BitScanReverse]] or LeadingZeroCount, which implicitly performs not only the isolation but also the [https://en.wikipedia.org/wiki/Binary_logarithm log2]. | ||

| − | '''Common MS1B''' | + | '''Common MS1B''' <br/> |

Two sets have a common MS1B, if the [[General Setwise Operations#Intersection|intersection]] is greater than the xor sum: | Two sets have a common MS1B, if the [[General Setwise Operations#Intersection|intersection]] is greater than the xor sum: | ||

<pre> | <pre> | ||

| Line 1,461: | Line 1,454: | ||

y = x * 0x00010100; | y = x * 0x00010100; | ||

</pre> | </pre> | ||

| − | '''Fill-Multiplication''' | + | '''Fill-Multiplication'''<br/> |

In fact, we can replace [[Parallel Prefix Algorithms|parallel prefix]] left shifts like, | In fact, we can replace [[Parallel Prefix Algorithms|parallel prefix]] left shifts like, | ||

<pre> | <pre> | ||

| Line 1,487: | Line 1,480: | ||

See [[Kindergarten Bitboards|Kindergarten-Bitboards]]- or [[Magic Bitboards|Magic-Bitboards]] as applications of fill-multiplication. | See [[Kindergarten Bitboards|Kindergarten-Bitboards]]- or [[Magic Bitboards|Magic-Bitboards]] as applications of fill-multiplication. | ||

| − | '''De Bruijn Multiplication''' | + | '''De Bruijn Multiplication''' <br/> |

| − | Another bitboard related application of multiplication is to determine the bit-index of the least significant one bit. A isolated, single bit is multiplied with a [[De Bruijn | + | Another bitboard related application of multiplication is to determine the bit-index of the least significant one bit. A isolated, single bit is multiplied with a [[De Bruijn Sequence]] to implement a [[BitScan#DeBruijnMultiplation|bitscan]]. |

<span id="Division"></span> | <span id="Division"></span> | ||

==Division== | ==Division== | ||

| Line 1,536: | Line 1,529: | ||

===Power of Two=== | ===Power of Two=== | ||

As a remainder, and to close the cycle to [[General Setwise Operations#Bitwisebooleanoperations|bitwise boolean operations]], the well known trick is mentioned, to replace modulo by power of two by [[General Setwise Operations#Intersection|intersection]] with power of two minus one: | As a remainder, and to close the cycle to [[General Setwise Operations#Bitwisebooleanoperations|bitwise boolean operations]], the well known trick is mentioned, to replace modulo by power of two by [[General Setwise Operations#Intersection|intersection]] with power of two minus one: | ||

| − | + | a % 2<span style="vertical-align: super;">n</span> == a & (2<span style="vertical-align: super;">n</span> - 1) | |

| − | a % 2 | ||

| − | |||

=Selected Publications= | =Selected Publications= | ||

| Line 1,547: | Line 1,538: | ||

* [[Mathematician#CSPeirce|Charles S. Peirce]] ('''1867'''). ''On an Improvement in Boole's Calculus of Logic''. Proceedings of the American Academy of Arts and Sciences, Series Vol. 7 | * [[Mathematician#CSPeirce|Charles S. Peirce]] ('''1867'''). ''On an Improvement in Boole's Calculus of Logic''. Proceedings of the American Academy of Arts and Sciences, Series Vol. 7 | ||

* [[Mathematician#Cantor|Georg Cantor]] ('''1874'''). ''[https://glossar.hs-augsburg.de/Cantor,_G._(1874):_Ueber_eine_Eigenschaft_des_Inbegriffs_aller_reellen_algebraischen_Zahlen Ueber eine Eigenschaft des Inbegriffes aller reellen algebraischen Zahlen]''. [https://en.wikipedia.org/wiki/Crelle%27s_Journal Journal für die reine und angewandte Mathematik], No. 77 | * [[Mathematician#Cantor|Georg Cantor]] ('''1874'''). ''[https://glossar.hs-augsburg.de/Cantor,_G._(1874):_Ueber_eine_Eigenschaft_des_Inbegriffs_aller_reellen_algebraischen_Zahlen Ueber eine Eigenschaft des Inbegriffes aller reellen algebraischen Zahlen]''. [https://en.wikipedia.org/wiki/Crelle%27s_Journal Journal für die reine und angewandte Mathematik], No. 77 | ||

| − | |||

* [[Mathematician#CSPeirce|Charles S. Peirce]] ('''1880'''). ''[https://archive.org/details/jstor-2369442 On the Algebra of Logic]''. [https://en.wikipedia.org/wiki/American_Journal_of_Mathematics American Journal of Mathematics], Vol. 3 | * [[Mathematician#CSPeirce|Charles S. Peirce]] ('''1880'''). ''[https://archive.org/details/jstor-2369442 On the Algebra of Logic]''. [https://en.wikipedia.org/wiki/American_Journal_of_Mathematics American Journal of Mathematics], Vol. 3 | ||

* [[Mathematician#Venn|John Venn]] ('''1880'''). ''[http://www.tandfonline.com/doi/abs/10.1080/14786448008626877#.U3kRnHYfwgI On the Diagrammatic and Mechanical Representation of Propositions and Reasonings]''. [https://en.wikipedia.org/wiki/Philosophical_Magazine Philosophical Magazine], Vol. 9, No. 5 | * [[Mathematician#Venn|John Venn]] ('''1880'''). ''[http://www.tandfonline.com/doi/abs/10.1080/14786448008626877#.U3kRnHYfwgI On the Diagrammatic and Mechanical Representation of Propositions and Reasonings]''. [https://en.wikipedia.org/wiki/Philosophical_Magazine Philosophical Magazine], Vol. 9, No. 5 | ||

* [[Mathematician#Venn|John Venn]] ('''1881'''). ''[https://archive.org/details/symboliclogic00venniala Symbolic Logic]''. MacMillan & Co. | * [[Mathematician#Venn|John Venn]] ('''1881'''). ''[https://archive.org/details/symboliclogic00venniala Symbolic Logic]''. MacMillan & Co. | ||

| + | ==1900 ...== | ||

| + | * [[Claude Shannon]] ('''1938'''). ''[https://en.wikipedia.org/wiki/A_Symbolic_Analysis_of_Relay_and_Switching_Circuits A Symbolic Analysis of Relay and Switching Circuits]''. [https://en.wikipedia.org/wiki/American_Institute_of_Electrical_Engineers Transactions of the AIEE], Vol. 57, No 12, Master's thesis 1940, [[Massachusetts Institute of Technology]] | ||

| + | * [[Mathematician#VIShestakov|Victor I. Shestakov]] ('''1941'''). ''Algebra of Two Poles Schemata''. [https://en.wikipedia.org/wiki/Automation_and_Remote_Control Automatics and Telemechanics], Vol. 5, No 2 | ||

==1950 ...== | ==1950 ...== | ||