Fairchild F8

Home * Hardware * Fairchild F8

Fairchild F8,

an 8-bit multi-chip microcontroller by Fairchild Semiconductor introduced and launched in 1975. The F8 consists of the 3850 CPU with 8-bit ALU, 64-bytes scratchpad RAM and two 8-bit I/O ports, the 3851 program storage unit (PSU) with 2 KiB ROM, the 3852 dynamic memory interface (MI), and 3853 static memory (or ROM) interface (SMI) chip, the optional 3854 DMA controller, and the 3861/3871 parallel I/O (PIO) chips. A minimal system could be build from a 3850 with either a 3851 or a 3853 with external ROM. The Mostek 3870 was a 3850/3851 single-chip implementation with some extra 64 bytes RAM, launched in 1977 [1] .

Details

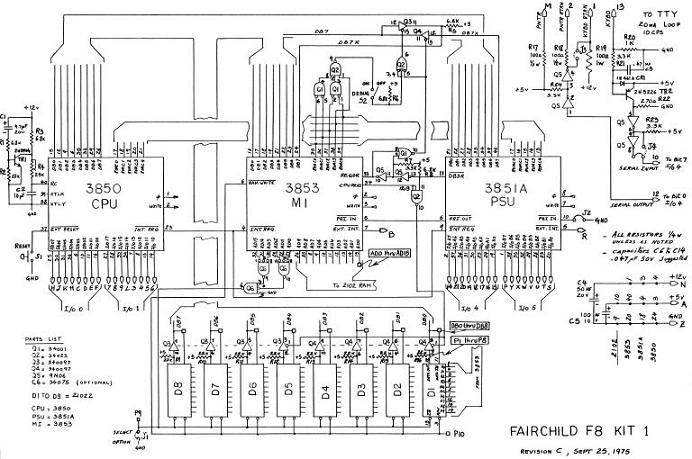

Circuit Diagram

F8 Kit circuit diagram [2]

Registers

The 3850 CPU has an 8-bit accumulator as input and output of the ALU, as well a 5-bit status register to indicate the flags sign, carry, zero and overflow after arithmetical and logical operations, as well as an interrupt control bit to enable or disable interrupts. The 64 byte scratchpad memory allow indirect addressing mode via the ISAR (indirect scratchpad register), which could be used as a kind of stack pointer to a stack frame of 8 bytes.

16-bit progam counter, stack register, data counter (DC to indirectly address up 64 KiB of memory), and address incrementer/adder were not part of the CPU, but in each PSU and/or MI. There is no address bus from the CPU, but a set of control signals, and transfer of addresses, i.e. branch targets, via the data bus. The stack register is directly linked to the program counter and simplifies the creation of a call stack.

Instructions

Arithmetical and logical instructions work on the accumulator. Source operands are either implicit, content of scratchpad register, indirect addressed via post-incremented data counter (DC) register, or immediate :

| Mnemonic | Description | Operation | Bytes | Cycles |

|---|---|---|---|---|

| NI ii | And with immediate | ACC &= ii | 2 | 2.5 |

| NS rn | And with scratchpad r0..63 | ACC &= rn | 1 | 1 |

| NM | And via post-incremented DC | ACC &= *DC++ | 1 | 2.5 |

Endianess

F8 is a big-endian machine concerning the byte-order of 16-bit words in (scratchpad) memory. For instance, LR PO,Q, restore Q register contents to the program counter, has the upper byte in scratchpad register r14, and the lower byte in r15.

Sample Assembly

A answer back program in F8 Assembly as given by David Edwards, Electronics Australia [3] :

ANSWER-BACK PROGRAM FOR MOSTEK F8 EVALUATION KIT D. EDWARDS, ELECTRONICS AUSTRALIA 19/10/76 0400 20 FF INIT,LI FF /LOAD AC WITH FF 0402 OB LR IS,A /INITIALIZE ISAR TO 3F 0403 54 LR 4,A /COPY AC INTO REG 4 0404 34 DS 4 /DECREMENT REG 4 TO FE 0405 56 LR 6,A /COPY AC INTO REG 6 0406 71 LIS H'1' /LOAD AC WITH 01 0407 B6 OUTS 6 /TRANSFER AC TO TIMER PORT TO ENABLE EXT INT 0408 1B EI /ENABLE I/O ROUTINES 0409 20 03 F3 START,PI 03F3 /CALL TTYIN SUBROUTINE 040C 4C LR AS /COPY CHAR INTO AC FROM RS 040D 25 OD CI 'OD' /COMPARE WITH CR 040F 84 06 BZ MESSAGE /JUMP TO MESSAGE IF CR 0411 28 03 5D PI 035D /SEND CHAR TO TTYOUT SUBROUTINE 0414 90 F4 BR START /LOOP BACK TO START 0416 2A 04 23 MESSAGE,DCI 0423 /LOAD DC WITH MESSAGE ADDRESS 0419 70 ANSWER,CLR /CLEAR AC 041A 88 AM /ADD CHAR TO AC AND INC DC 041B 84 ED BZ START /LOOP BACK TO START 041D 5C LR S,A /COPY CHAR INTO RS 041E 28 03 5D PI 035D /SEND CHAR TO TTYOUT SUBROUTINE 0421 90 F7 BR ANSWER /LOOP BACK TO ANSWER 0423 OD 47 4F /START OF ANSWER BUFFER 0426 20 41 57 0429 41 59 2C 042C 20 49 27 043F 4D 20 42 0432 55 53 59 0435 21 OD 00 /ANSWER MUST END WITH A ZERO BYTE

F8 Chess Computers

The original CompuChess [4] and its clone, the Novag Chess Champion MK I had the 3850 CPU and the 3853 SMI, addressing a 2 KiB 2316 compatible ROM, and 2 x 2111 [5] 256x4 each, in total 256 byte SRAM [6] . Boris also used the 3850/3853 approach with 2 x 2112 for 256 byte SRAM, and 2 x 2 KiB ROM [7] . David Kittinger had to solve the 128 byte challenge (including scratchpad) for the Novag Micro Chess with Mostek 3870.

External Links

- Fairchild F8 from Wikipedia

- Fairchild processor - BORIS IS KING

- Fairchild F8 (3850) microcontroller family from CPU world

- CPU of the Day: Fairchild F8 Microprocessor | The CPU Shack Museum, June 8, 2013

- Mostek 3870 (MK3870) microcontroller family from CPU world

- Patent US4086626 - Microprocessor system - Google Patents

- F8 info by Sean Riddle

- Fairchild Channel F from Wikipedia

- the dasm macro assembler

- asmx multi-CPU assembler

References

- ↑ Mostek 3870 (MK3870) microcontroller family from CPU world

- ↑ Fairchild F8 Kit 1 Schematic, Revision C, 25 Sep 1975, User Manual Wiki

- ↑ David Edwards (1976). The Mostek F8. Electronics Australia, December, 1976

- ↑ CompuChess from Schachcomputer.info - Wiki by Mike Watters

- ↑ MM2111 pdf, MM2111 description, MM2111 datasheets, MM2111 view

- ↑ Novag Chess Champion MK I from Schachcomputer.info - Wiki (German)

- ↑ Boris assembly manual (pdf) hosted by Alain Zanchetta