DEC Alpha

DEC Alpha,

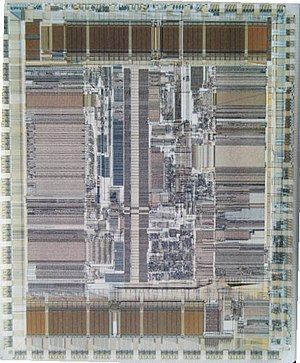

a 64-bit RISC processor developed by Digital Equipment Corporation designed to replace their 32-bit VAX instruction set. The 21064 was the first Alpha processor introduced as DECchip 21064, code named EV4, in February 1992 [2], released since September 1992. While Alpha processors were widely used through the 90s in Workstations and Server, such as DEC 3000 AXP, AlphaStation and AlphaServer, running OpenVMS, Digital UNIX and even Windows NT, Cray Research used the 150 MHz Alpha 21064 in their Cray T3D supercomputer.

The Alpha architecture was sold, along with most parts of DEC, to Compaq in 1998. Compaq, already an Intel customer, decided to phase out Alpha in favor of the forthcoming Itanium architecture, and sold all Alpha intellectual property to Intel in 2001 [3].

Contents

Architecture

The Alpha 21064 is a superpipelined dual-issue superscalar microprocessor that executes instructions in-order. It is capable of issuing up to two instructions every clock cycle to four functional units: an integer unit, a floating-point unit (FPU), an address unit, and a branch unit. The integer pipeline is seven stages long, and the floating-point pipeline ten stages. The first four stages of both pipelines are identical and are implemented by the I-Box. The 21064 implemented a 43-bit virtual address and a 34-bit physical address, and is therefore capable of addressing 8 TiB of virtual memory and 16 GiB of physical memory.

Data Types

In the Alpha little-endian [4] architecture, a byte is defined as octet, a word as a 16-bit datum, a longword as a 32-bit datum, a quadword as a 64-bit datum, and an octaword as a 128-bit datum. Floating-point types are either 32-bit floats or 64-bit doubles, IEEE 754 as well as VAX floating point format for backward compatibility.

Register File

The Alpha instruction set architecture (ISA) defined a set of 32 64-bit integer registers R0 .. R31, and 32 64-bit floating point registers F0 .. F31, where R31 and F31 were not writable and handwired to zero. The 64-bit program counter is longword aligned and incremented by four to the address of the next instruction when an instruction is decoded. A lock flag and locked physical address register are used by the load-locked and store-conditional instructions for multiprocessor support.

Integer Instructions

The integer arithmetic instructions perform addition, multiplication, and subtraction on longwords or quadwords, comparison on quadwords, and conditional move instructions. Signed and unsigned compare instructions compare two registers or a register and a literal and write '1' to the destination register if the specified condition is true or '0' otherwise. Bitwise logical instructions perform AND (Logical Product), OR (Logical Sum, BIS), and XOR (Logical Difference), while the instructions with the mnemonics BIC, ORNOT and EQV use the complement of the second source operand. Shift instructions perform arithmetic right shift, and logical shift in both directions.

Count Extensions

The Count Extensions (CIX) was an integer extension of three instructions for population count and bitscan purposes, first implemented on the Alpha 21264A (EV67) in late 1999 [5].

| Mnemonic | Instruction |

|---|---|

| CTLZ | Count Leading Zero |

| CTPOP | Count Population |

| CTTZ | Count Trailing Zero |

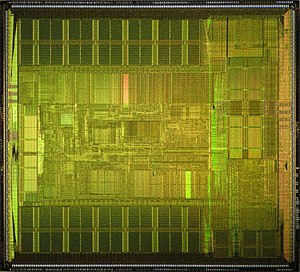

21164

The Alpha 21164 (EV5) was introduced in January 1995. It is a four-issue superscalar processor capable of issuing a maximum of four instructions per clock cycle to two integer and two floating-point execution units. The integer pipeline is seven stages long, and the floating-point pipeline is ten stages long. The 21164 implemented a 43-bit virtual address and a 40-bit physical address. The two integer pipelines, add and multiply, are both capable of executing add, logical, load, compare, and conditional move instructions. The multiply pipeline exclusively executes shift, store, and multiply instructions. The add pipeline exclusively executes branch instructions. The 21164 has three levels of cache, two on-die and one external and optional. The primary cache is split into separate caches for instructions and data, referred to as the I-cache and D-cache respectively. They are 8 KB in size, direct-mapped and have a cache line size of 32 bytes. Cray Research used the 300 MHz Alpha 21164 in their Cray T3E supercomputer.

21264

The Alpha 21264 (EV6), introduced in October 1996, is a four-issue superscalar processor with out-of-order execution, speculative execution and a seven-stage instruction pipeline. It has a peak execution rate of six instructions per cycle. The Alpha 21264 has two levels of cache, a primary cache and secondary cache. The three-level cache of the Alpha 21164 was not used due to problems with bandwidth [7].

Chess Programs

at times running on DEC Alpha

See also

Manuals

- DIGITAL UNIX Documentation - Programming Guides

- Alpha Architecture Reference Manual (pdf) Compaq

- Digital UNIX Assembly Language Programmer's Guide, March 1996 (pdf)

Publications

- Richard L. Sites (1992). Alpha AXP Architecture. Digital Technical Journal, Vol. 4, No. 4, pdf

Forum Posts

- Alpha Architecture Technical Summary by Jim Gettys, comp.arch, February 25, 1992

- Crafty on 767Mhz Alpha at Paris WMCCC? by Richard A. Fowell, rgcc, September 27, 1997

- Question to Bob: Crafty , Alpha and FindBit() by Guido Schimmels, CCC, June 05, 1998 » Crafty, BitScan

External Links

- DEC Alpha from Wikipedia

- Alpha Instruction Set (Brief)

- Alpha instruction-set specification

- Alpha: The History in Facts and Comments by Paul V. Bolotoff, April 2005

- Alpha/FAQ - Gentoo Wiki [8]

Processors

- Alpha 21064 from Wikipedia

- Alpha 21164 from Wikipedia

- Alpha 21264 from Wikipedia

- Alpha 21364 from Wikipedia

Workstations

Server

References

- ↑ Die photo of Alpha AXP 21064, by Dyl, April 02, 2007, DEC Alpha from Wikipedia, Alpha 21064 from Wikipedia, CC-BY-SA

- ↑ Alpha Architecture Technical Summary by Jim Gettys, comp.arch, February 25, 1992

- ↑ DEC Alpha from Wikipedia

- ↑ Alpha/FAQ - Is Alpha big endian or little endian?

- ↑ Question to Bob: Crafty , Alpha and FindBit() by Guido Schimmels, CCC, June 05, 1998

- ↑ English: Die shot of DEC Alpha 21164 (EV5) microprocessor, by Pauli Rautakorpi, 28 June 2013, Alpha 21164 from Wikipedia, CC BY 3.0

- ↑ Alpha 21264 - Cache - Wikipedia

- ↑ Gentoo Linux from Wikipedia