I860

i860, (80860)

was a 32/64-bit RISC microprocessor introduced in 1989 by Intel. The first i860 XR ran at 25, 33, or 40 MHz. The second generation i860 XP added larger on-chip first level caches, second level cache support, and hardware support for bus snooping for cache consistency in multiprocessor systems [2]. Due to several performance problems, the i860 never achieved commercial success and the project was abandoned in the mid-1990s.

Architecture

The processor had a VLIW architecture with two pipelines [3], a 32-bit integer ALU "core", and a three part 64-bit FPU or SIMD unit consisting of an adder, multiplier, and a 3D-graphics unit. Core integer execution was applied using 32 32-bit registers r0 through r31, also used for address computation. IEEE 754 floats or vectors of bytes and words are kept in 32 32-bit registers f0 through f31, which can also be configured as 16 x 64 (i.e. for IEEE 754 double) or 8 x 128-bit vector registers. When accessing 128-bit values, a aligned set of four registers was used, addressed by f0, f4, ..., f28. The i860 FP and SIMD design influenced the later MMX extension of x86 processors, the Pentium MMX in 1998.

Paragon

The Paragon was a series of massively parallel supercomputers by Intel based on the i860. Up to 2048 (later, up to 4000) i860s were connected in a 2D grid.

Chess Programs

Manuals

- Intel® i860™ Microprocessor Family Programmer's Reference Manual 1991 (pdf from bitsavers.org)

- David Perlmutter, Michael Kagan (1991). The i860™ XP Second Generation of the i860™ Supercomputing Microprocessor Family. pdf

External Links

- Intel i860 from Wikipeida

- The Chip Collection - i860 Microprocessor, Smithsonian Institution

- Intel 80860 (i860) CPU family

- From Here to There - Intel i860 by Mike Garrity, April 06, 2010

- Intel Paragon from Wikipedia

References

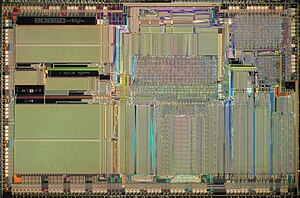

- ↑ Die shot of Intel 80860XR microprocessor (A80860XR-40, SX438) by Pauli Rautakorpi, April 25, 2014, CC BY 3.0, Wikimedia Commons, Intel i860 from Wikipedia.de (German)

- ↑ Intel i860 from Wikipeida

- ↑ From Here to There - Intel i860 by Mike Garrity, April 06, 2010