CHEOPS

CHEOPS,

a Chess-Oriented Processing System with a dedicated chess processor, developed end of the 70s at MIT by John Moussouris, Jack Holloway and Richard Greenblatt, derived from the original conception and design of a 8x8 hardware chess array instrumented by Edward Fredkin. CHEOPS was used by Baisley's Tech 2 and a brute force version of Greenblatt's Mac Hack [2], but unfortunately have never competed in computer chess tournaments with this approach. According to Joe Condon and Ken Thompson, already working on a chess hardware for Belle, the problem with CHEOPS was the lack of positional evaluation support [3].

Contents

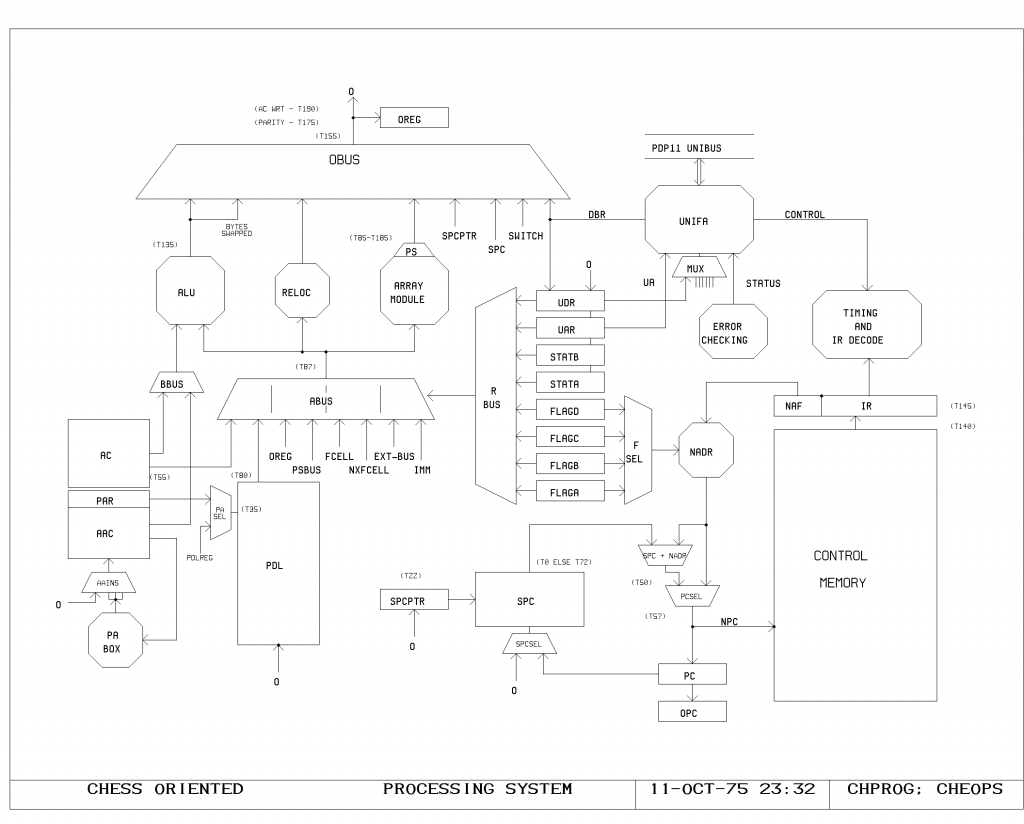

Block Diagrams

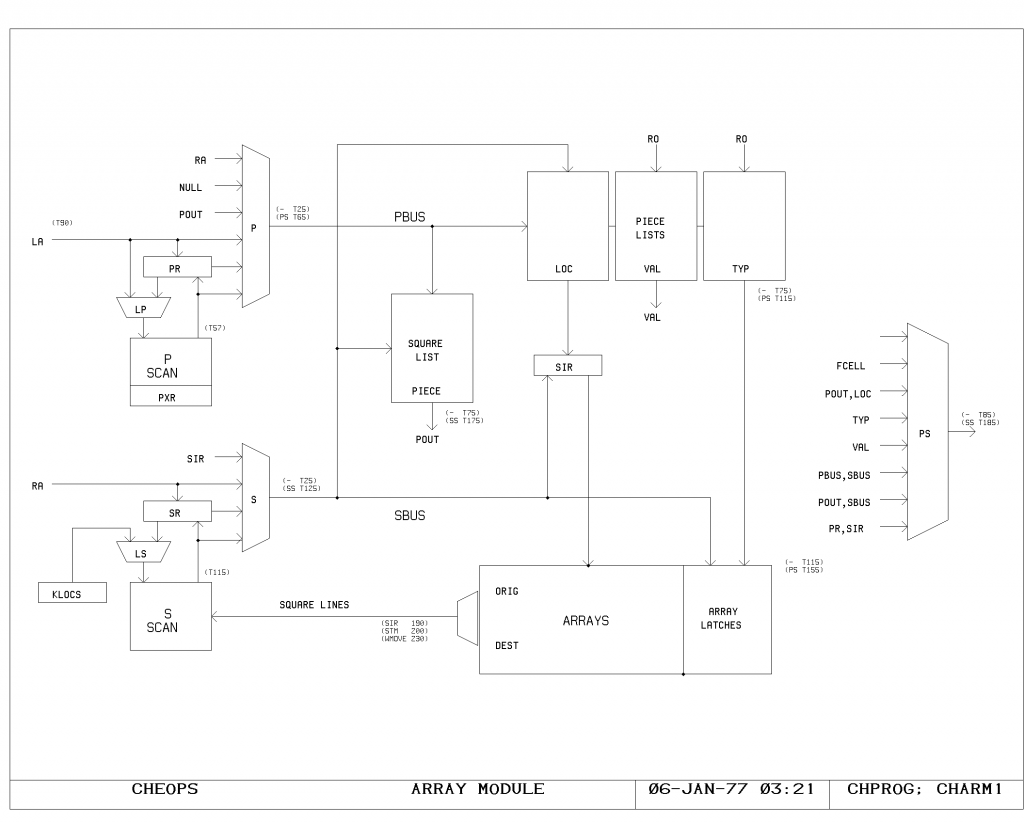

CHARM

CHEOPS had all components of a general purpose processor, in addition to a 16-bit ALU, it had a powerful Chess Array Module (CHARM), which contains a board representation and most of the chess specific logic for attack and move generation including transformation of a piece-list to a hardwired bitboard and from bitboards to a list of squares or moves. Like the ALU, CHARM's input is connected via the ABUS with a 1024-word push down list (PDL). For example CHARM can accept a record from the PDL of the last move tried from a given position, and generate the next possible move in a specified order. In general, the 8x8 CHARM chess array module is to find a specified subset of legal board moves.

The Chess arrays

Each of the 64 squares retains information about the color and type of piece (if any) occupying it. Beside memory to keep the board and pieces, the chess array contains the combinatorial logic for each square, controlled by various signal lines. It may generate attacks and sets of legal moves to one designated destination square, where the output consists of 64 lines which specify which of the 64 squares contain pieces of the moving color which can capture or move to that destination.

Alternatively, a square can be designated as the originating-area, in which case the 64 lines assert possible destinations for moves from this square, a hardwired move target bitboard. Special control bits can cause the array functions to be more specific or general. It can discriminate captures from non-capturing moves, or pawn from noble capture, or cause the entire board to be designated as originating or destination area, so that general questions as "any capture possible?" can be answered in a single operation.

The Array module

The array module consists of a sequential logic to implement the inner loops of typical move generation routines in scanning squares and pieces, in particular it implements the bitboard serialization to convert the 64 square output lines from the chess arrays to an internal list of squares. The BitScan hardware has the 64 square lines and a "last square number" register as input, to generate the number of the next active square line.

Micro-Controller

The sequence of ALU and CHARM operations in CHEOPS is determined by a 1K by 64 bit RAM control memory. Each micro-instruction consists of four 16-bit words. A cycle time of the machine is about 180 nanoseconds. The remainder of the CHEOPS system consists of a PDP-11 and a time shared PDP-10 which communicate with the special processor through a special bus interface.

Publications

- John Moussouris, Jack Holloway, Richard Greenblatt (1979). CHEOPS: A Chess-orientated Processing System. Machine Intelligence 9, reprinted (1988) in Computer Chess Compendium

See also

Namesakes

- Cheops (CHEss OPponent Simulator) by Tristan Miller [4]

External Links

- PDP-10 software for controlling CHEOPS: CHPROG; CCHEOP 484 hosted by Lars Brinkhoff

- CHEOPS microcode source: AGB; CHUCOD 83 hosted by Lars Brinkhoff

References

- ↑ Great Pyramid of Giza, Photo by Nina Aldin Thune, March 2005, Wikimedia Commons

- ↑ John Moussouris, Jack Holloway, Richard Greenblatt (1979). CHEOPS: A Chess-orientated Processing System. Machine Intelligence 9, reprinted (1988) in Computer Chess Compendium

- ↑ Joe Condon, Ken Thompson (1982). Belle Chess Hardware. Advances in Computer Chess 3, Reprinted (1988) in Computer Chess Compendium

- ↑ CHEOPS - nothingisreal.com